Definicon

Definicon was in the beginning an US-based software company writing scientific programs. Later they found out that available computers did not perform as promised. Therefore they decided to build their own machine. But to build a computer from scratch is a big job. It would be better to reuse some existing hardware.

Around 1984 it was already clear that the PC would became a dominant computing platform. Part of the success story was the 8-bit ISA bus. Originally defined for I/O extensions Definicon had the brilliant idea to put a powerful processor together with memory on an I/O board. The concept of the coprocessor was born. The processor of the PC was then only responsible for I/O tasks.

Definicon offered in 1985 the DSI-32 coprocessor board for the PC. Three key people had done most of the job. Trevor Marshall and Georg Scolaro did the vast majority of the hardware design. David Rand programmed the operating system and ported the well known Green Hills compilers. In addition he wrote most of the manuals. Georg Scolaro did also the assembler and linker.

To deliver the desired computing power the DSI-32 used the NS32032 CPU and the NS32081 FPU at 10 MHz clock speed and 1 Mbyte memory in the standard configuration. To support Unix the board had a socket for the NS32082 MMU. Surprisingly the socket for the MMU could be used for the NS32016 CPU with the help of some jumpers. In this case the NS32032 had to be removed. The 16-bit NS32016 could only use half of the memory. This was the very low-cost option. In the US the price for the standard configuration was $1495. In Great Britain the price was around £500 in 1987. Another option using a 6 MHz NS32032 and NS32081 and 256 kbyte memory build with 64-kbit DRAMs was available for $995.

In August and September 1985 the Byte magazine printed two articles about the DSI-32. Part 1 explained the hardware and part 2 covered the software. The level of detail in the hardware description allowed an easy rebuild of the system (see Systems/Richard).

At archive.org the articles are available:

- The DSI-32 Coprocessor Board. Part 1: The Hardware at page 120

- The DSI-32 Coprocessor Board. Part 2: The Software at page 116.

In May 2016 I got the first photo of a DSI-32 board. Thanks to Graham! He bought it 2nd hand before 2000 together with some software including the C compiler.

Fig. 1. The Definicon DSI-32 coprocessor board using an 8-bit ISA connector.

It is astonishing how similar are the boards of Definicon and Opus, who was another vendor of Series 32000 coprocessor boards (see Systems/Opus). But the designs were not software compatible!

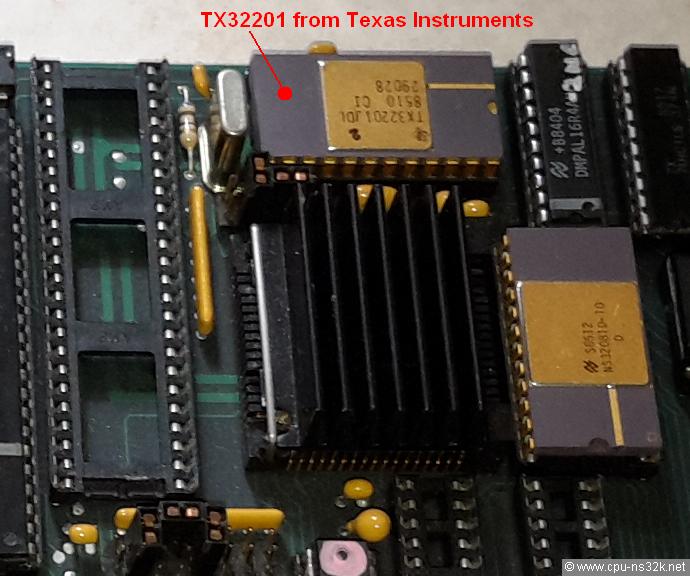

Fig. 2. The heart of the board is placed below the heatsink: the NS32032 CPU. The TX32201 is something special, see Chips/Second Source.

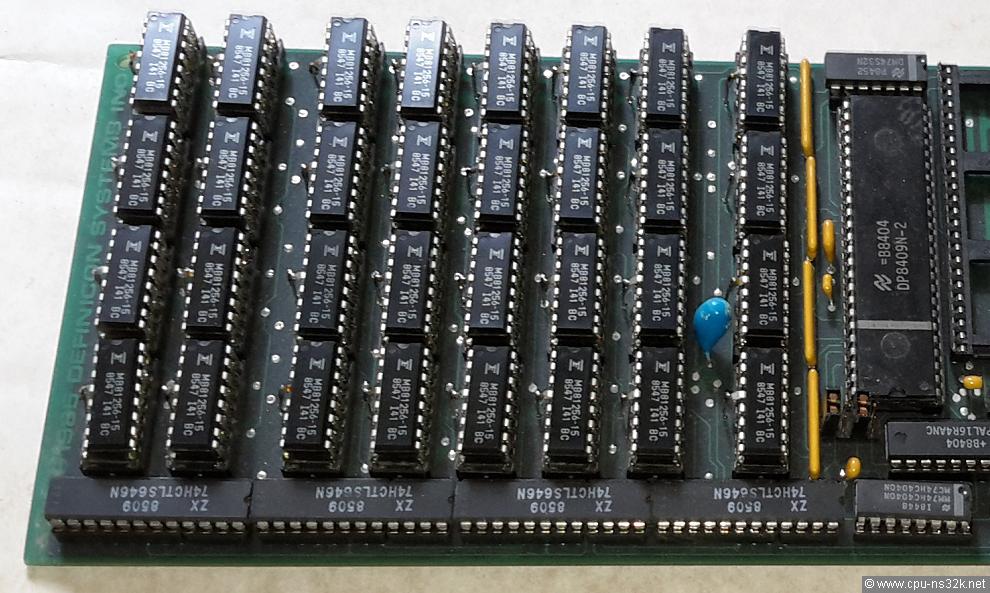

Graham's board has a special feature. It has 2 Mbytes of DRAM. But there are only 32 sockets for 256-kbit DRAMs. Therefore Definicon soldered on each DRAM another DRAM. This could be done easily with DIP packages. Pin 4 of the little DRAM tower must be used independent. Pin 4 gets the signal RAS (Row Address Strobe) which is used as a bank select signal. Two RAS signals are generated by the memory controller.

Fig. 3. A detailed look at the memory array with the memory controller DP8409N-2 on the right side.

Defincon recognized early that a large memory array was important for the intended applications. Therefore they made a 2 Mbytes version of the DSI-32 board with the holes to connect a second RAS signal already there. But the special "double stack" sockets were not available at the time they had to ship the 2 Mbytes version. To be able to deliver they used the solder solution and tested the boards very well. Later boards did use the more common ram sticks and they also used ZIP memory.

I'm curious to see the "double stack" socket. Today you find nothing about this kind of socket in the internet. Maybe someone has a board with this socket or someone has a datasheet. Of course both would be best.

The four long chips at the lower edge in Figure 3 are data bus buffers from the company ZX. I don't know the manufacturer. His naming of the chips is somehow irritating. Is 74HCTLS646N a CMOS (=HCT) chip or a bipolar (=LS) chip or both? David Rand knows the answer: it is CMOS. He also explained why the NS32201 TCU (or TX32201) is mounted on the top: the device is getting very hot.

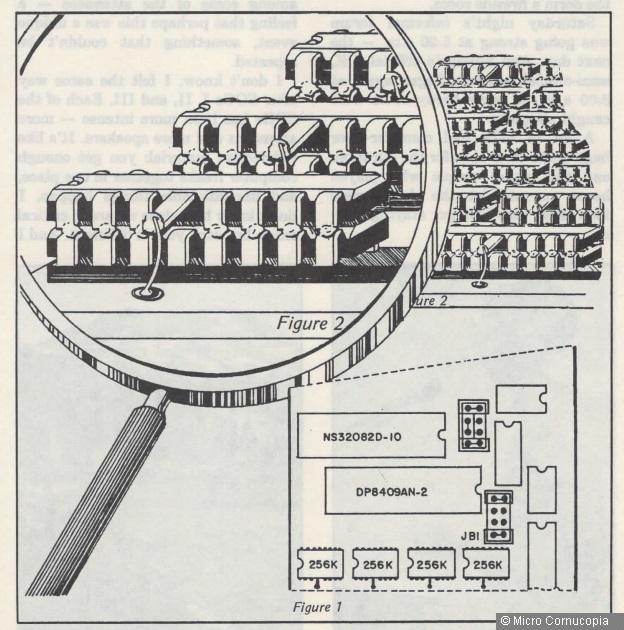

In August 2017 Michael sent me an article of the Micro Cornucopia magazine, issue 26 from 1985. It described what to do to upgrade the memory of the cheapest DSI-32 board. The result looks like what the photo in Figure 3 shows. The nice drawing of the article is presented in Figure 4. The article is available here:

Two Megabytes And More On The DSI-32

Fig. 4. This drawing was found in Micro Cornucopia, Number 26, October-November 1985.

Thanks to David Rand who contributed to this chapter.

Another version of the board

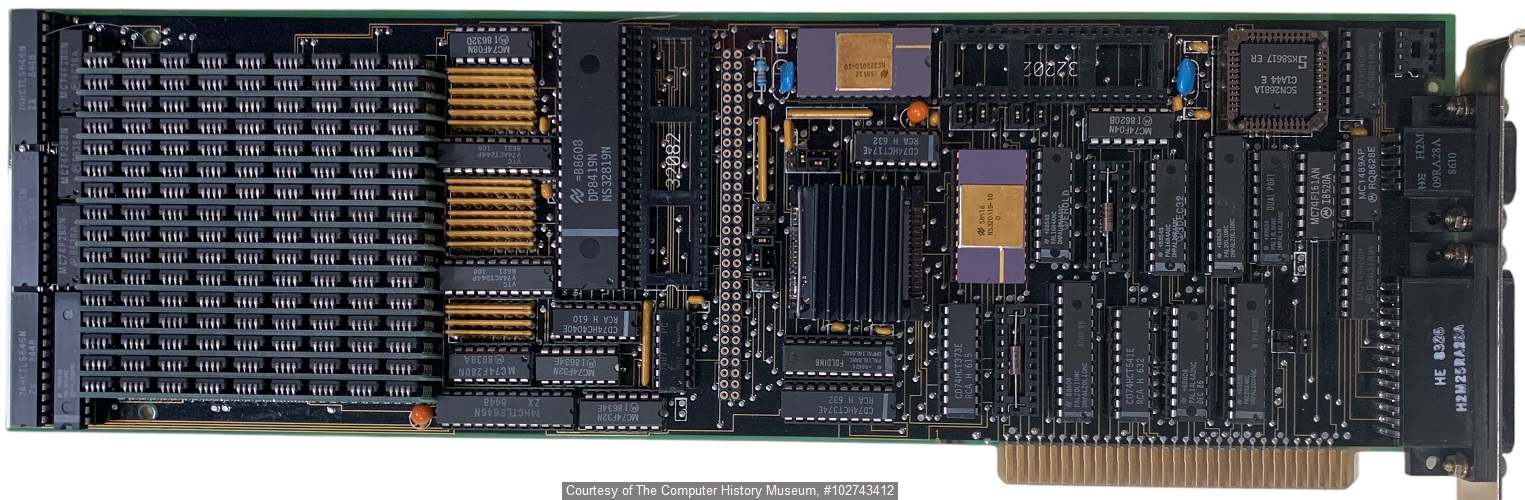

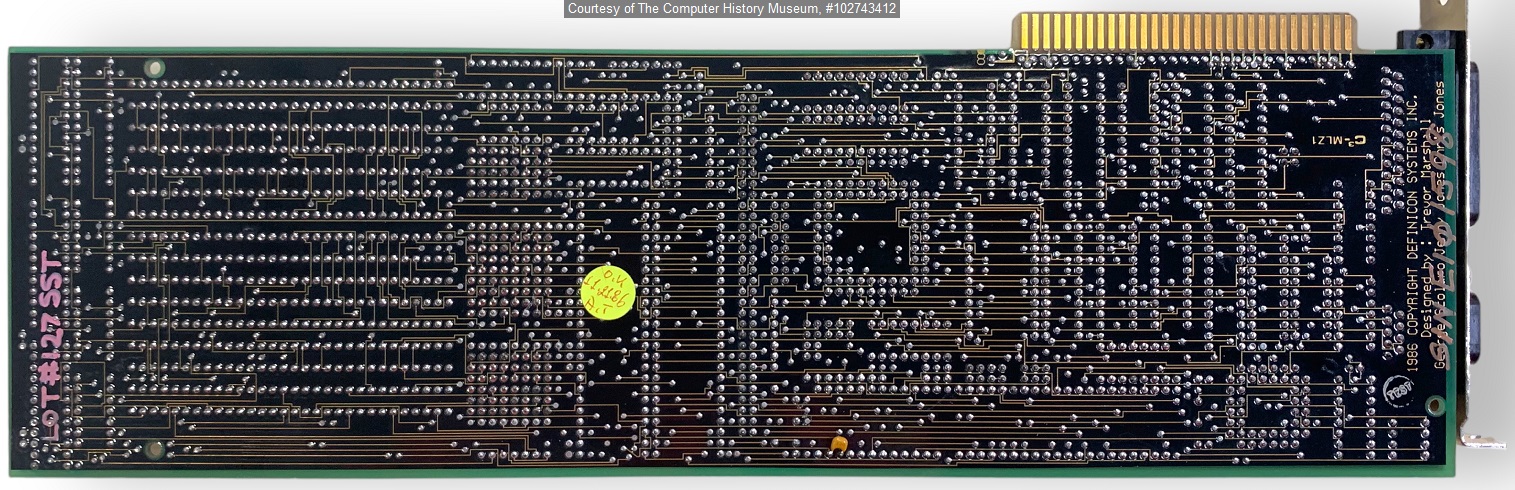

In February 2023 I saw a different version of the board in Figure 1 at the Computer History Museum (CHM). Their photo was quite small. I asked for a bigger one and they responded with some pretty good photos - thank you very much!

This version of the board is obviously a newer one. It uses 16 memory modules instead of DIP devices so that Definicon could pack 4 Mbytes of parity protected DRAM on the board. More memory is always good. But it has a significant drawback: the price. I have no idea about the price of such a memory module in the 1980s but it was for sure not cheap.

Fig. 5. This board contains 144 DRAMs in the smallest space. A lot of resistor arrays are placed between the memory controller DP8419 and the memory array.

Fig. 6. At the right end of the backside one can find the name of the designers and the year of production.

The routing on the PCB looks not like it was done by a human being.

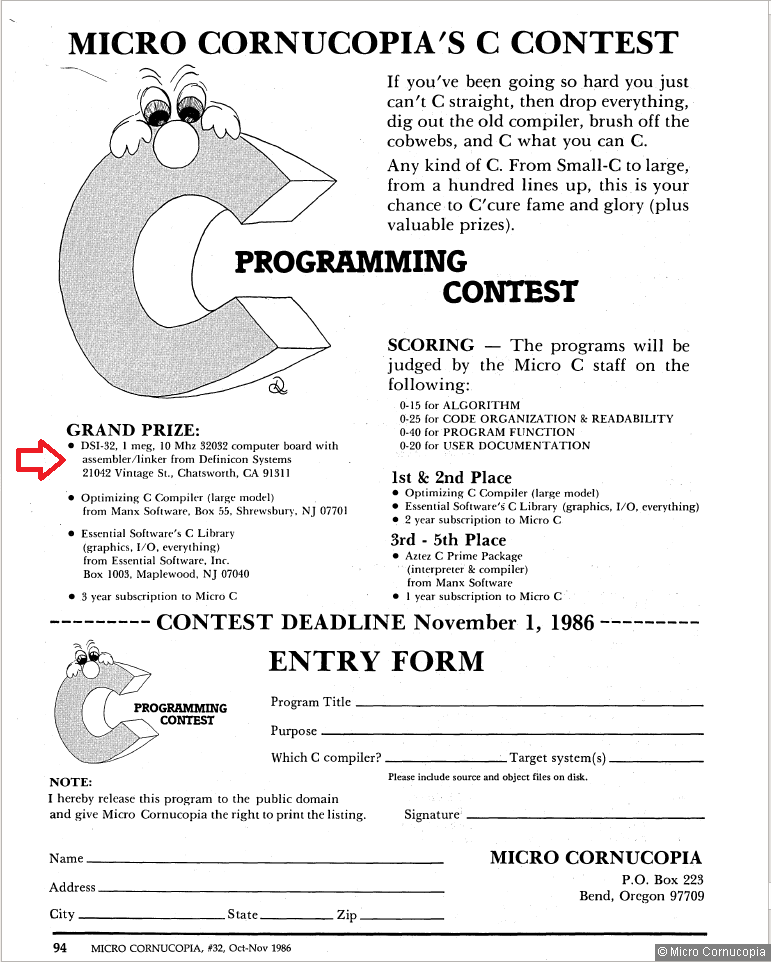

GRAND PRIZE

In October 1986 Micro Cornucopia announced a C contest. There was not only a prize for being first to fifth but also a grand prize. The grand prize included hardware in the form of a DSI-32 board. I like this prize. But what would you do if you are not a skilled programmer? Today you can ask ChatGPT. But in 1986? I would have no chance 🙁

Fig. 7. This is the page about the C contest. I have added the red arrow to point to the hardware prize.

Marco

In December 2025 I got an email from Marco. He told me that he uses a DSI-32 board for program development, not for fun but for professional use - in 2025 and very probably also in 2026 !

I was very surprised. The reason is that Marco worked in a company which uses Programmable Logic Controllers (PLC) to control industrial processes. And their PLCs use Series 32000 CPUs!

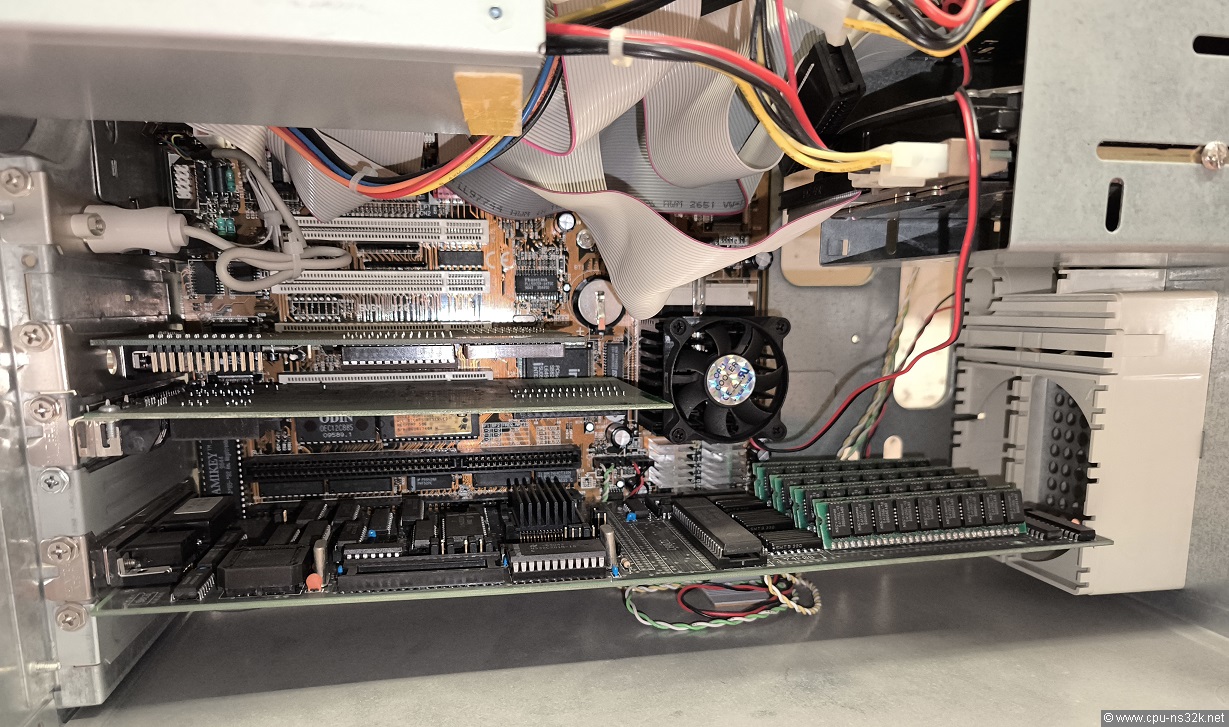

The host system for the DSI-32 is an old Pentium PC still running MS-DOS (never change a running system 😊). The PC has a 2 GByte hard disk. Only 20 MByte are in use. And the PC has a network card - he must not use floppy disks to transfer data.

Fig. 8. Marco's Pentium PC with the DSI-32 board inserted.

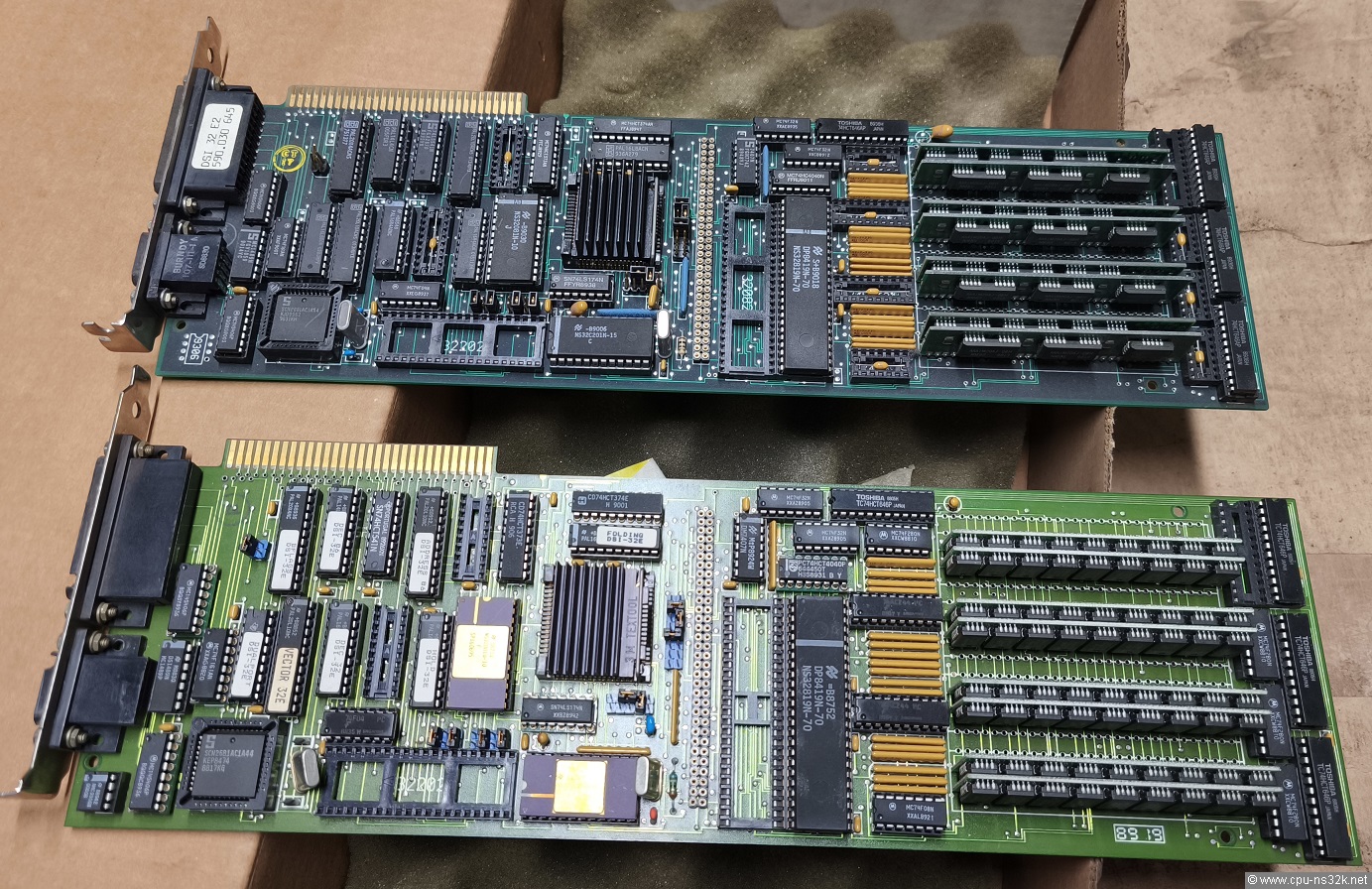

Fig. 9. Marco has two more DSI-32 boards. A comfortable situation in case there is a problem with the used board.

The upper board in Figure 9 misses two buffers for the DRAMs and the four parity logic chips 74280. If Marco must use this board he can take the chips from another board.

It is interesting that I have never seen a DSI-32 board with the NS32202 ICU or the NS32082 MMU inserted. The board in use has even not the socket for the MMU. It also misses the 7408 right to the DRAM controller DP8419 together with its socket. Obviously it is optional logic because the board is running...

This chapter was last modified on 22 January 2026. Next chapter: Delta Instrumentation