# Overflow Conditions in CMACD Instruction Execution on NS32GX320

## **1.0 INTRODUCTION**

This application note describes how to handle overflow occurrence in the CMACD (Complex Multiply and Accumulate Double) instruction in the NS32GX320. It includes a description of cases in which overflow occurs in the CMACD instruction, and provides examples of these cases.

## 2.0 DESCRIPTION

#### 2.1 A General Description of Overflow in Addition Operations

Overflows occur in addition operations when the carry bit into the sign bit position disagrees with the carry bit out of the sign bit position. When this happens, the correct result is too large to be to represented as a signed integer number, and is often represented by the wrong sign. Thus, the overflow of two positive numbers yields a negative number, while the overflow of two negative numbers yields a positive number.

## 2.2 Examples of Overflow in Addition Operations

This section provides two examples of overflows in addition operations with two 8-bit numbers. The first example shows what happens when two positive numbers are added. The second example shows what happens when two negative (2's complement) numbers are added.

Example A: Adding Two Positive Numbers

$\rightarrow$  carry bit = 0  $\rightarrow$  Overflow

This example shows how adding two positive operands  $(01000101 = 69 \text{ decimal}, 01001010 = 74 \text{ decimal}) \text{ produces a negative result (10001111 = -113 \text{ decimal}).}$

National Semiconductor Application Note 720 Yair Hadas August 1990

$\rightarrow$  carry bit = 1  $\rightarrow$  Overflow

This example shows how adding two negative operands (10001101 = -115 decimal, 10000111 = -121 decimal) produces a positive result: (00010100 = 20 decimal).

### 3.0 STANDARD OVERFLOW IN CMACD

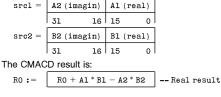

The Complex Multiply and Accumulate Double (CMACD) instruction reads two double-word source operands, representing complex numbers. Each operand consists of a signed 16-bit real part in the low-order word and a signed 16-bit imaginary part in the high-order word. The result consists of a signed 32-bit real part in R0, and a signed 32-bit imaginary part in R1.

The instruction syntax is: CMACD srcl. src

As

| MACD    | srcl,  | src2   |

|---------|--------|--------|

|         | gen    | gen    |

|         | read.D | read.D |

| suming: |        |        |

|         |        |        |

R1 := R1 + A1 \* B2 + A2 \* B1 -- Imaginary result

The CMACD instruction consists of three ADD operations and one SUB operation. The overflow can occur during each of these operations.

Following is the order of additions and subtractions in the execution of a CMACD instruction:

- a. R1 + A2 \* B1

- b. R0 A2 \* B2

- c. (R1 + A2 \* B1) + A1 \* B2

- d. (R0 A2 \* B2) + A1 \* B1

The following section gives 8 examples of this standard type of overflow occurrence. Section 4.0 will give 4 examples of a more complicated type of overflow occurrence.

AN-720

Overflow Conditions in CMACD Instruction Execution on NS32GX320

© 1995 National Semiconductor Corporation TL/EE11064

RRD-B30M75/Printed in U. S. A

4.0 EXAMPLES OF STANDARD OVERFLOW Example 1: Overflow on R1 + A2 \* B1 when A2 \* B1 is Positive In this operation, an overflow occurs when the product of A2 and B1 is added to R1. = 60000000 # rl a2 \* bl # = 31000000  $rl + a2 * bl = 91000000 \rightarrow overflow$ # ovfl: movd \$h' 6000000, rl movd \$h' 70000001, r2 \$h' 00017000, r3 movd cmacd r2, r3 Here is what happens when the operation reaches the CMACD. (Note that A2 and B1 appear in italics.): srcl src2 A2 \* B1 rl  $\rightarrow$  carry bit = 1  $\rightarrow$  carry bit = 0  $\rightarrow$  Overflow Example 2: Overflow on R1 + A2 \* B1 when A2 \* B1 is Negative In this operation, an overflow occurs when the product of A2 and B1 is added to R1. # rl = b0000000a2 \* bl # = c000ffff  $rl + a2 * bl = 7000 ff ff \rightarrow overflow$ # ovf2: movd \$h' b0000000, rl movd \$h' 7fff0001, r2 movd \$h' 00018001, r3 cmacd r2, r3 Here's what happens when the operation reaches the CMACD. (Note that A2 and B1 appear in italics.): srcl = 0000000000000110000000000000000 src2 a2 \* bl = 11000000000000011111111111111 rl rl + a2 \* bl = 0111000000000011111111111111  $\rightarrow$  carry bit = 0  $\rightarrow$  carry bit = 1  $\rightarrow$  Overflow Example 3: Overflow on (R1 + A2 \* B1) + A1 \* B2 when A1 \* B2 is Positive In this operation an overflow occurs when the product of A1 and B2 is added to R1 + A2 \* B1. # rl = 20000000 a2 \* bl = 31000000# rl \* a2 \* bl # = 51000000 al \* b2 = 4000000 #  $rl + a2 * bl + al * b2 = 91000000 \rightarrow overflow$ # ovf3: movd \$h' 20000000, rl movd \$h' 70008000, r2 movd \$h' 80007000, r3 cmacd r2, r3

2

```

Example 4: Overflow on (R1 + A2 * B1) + A1 * B2 when A1 * B2 is Negative

In this operation an overflow occurs when the product of A1 and B2 is added to R1 + A2 * B1.

= c0000000

#

rl

a2 * bl

#

= c000ffff

rl * a2 * bl

#

= 8000ffff

al * b2

#

= f0000000

rl + a2 * bl + al * b2 = 7000 ffff \rightarrow overflow

#

ovf4: movd $h' c0000000, rl

movd $h' 7fff4000, r2

movd $h' c0008001, r3

cmacd r2, r3

Example 5: Overflow on R0 - A2 * B2 when A2 * B2 is Positive

In this operation an overflow occurs when the product of A2 and B2 is subtracted from R0.

r0

= 60000000

#

a2 * b2

= c000ffff

#

r0 - a2 * b2 = 9fff0001 \rightarrow overflow

#

ovf5: movd $h' 60000000, r0

movd $h' 7fff0001, r2

movd $h' 80010001, r3

cmacd r2, r3

Example 6: Overflow on R0 - A2 * B2 when A2 * B2 is positive.

In this operation an overflow occurs when the product of A2 and B2 is subtracted from R0.

#

r0

= b0000000

a2 * b2

= 3fff0001

#

#

r0 - a2 * b2 = 7000ffff \rightarrow overflow

ovf6: movd $h' b0000000, r0

movd $h' 7fff0001, r2

movd $h' 7fff0001, r3

cmacd r2, r3

Example 7: Overflow on (R0 - A2 * B2) + A1 * B1 when A1 * B1 is positive.

In this operation an overflow occurs when the product of A1 and B1 is added to R0 - A2 * B2.

= 70000000

#

rl

a2 * b2

#

= 10000000

r0 - a2 * b2

= 6000000

#

al * bl

= 31000000

#

r0 - a2 * b2 + al * bl = 91000000 \rightarrow overflow

#

ovf7: movd $h' 70000000, r0

movd $h' 40007000, r2

movd $h' 40007000, r3

cmacd r2, r3

Example 8: Overflow on (R0 - A2 * B2) + A1 * B1 when A1 * B1 is negative.

In this operation an overflow occurs when the product of A1 and B1 is added to R0 - A2 * B2.

= c0000000

#

r0

a2 * b2

= 10000000

#

r0 - a2 * b2

= b0000000

#

al * bl

= c000ffff

#

r0 - a2 * b2 + al * bl = 7000ffff \rightarrow overflow

#

ovf8: movd $h' c0000000, r0

movd $h' 40007fff, r2

movd $h' 40008001, r3

cmacd r2, r3

```

5.0 COMPLICATED OVERFLOW IN CMACD There are two cases when the final result is correct although the overflow flag is set. These are the cases in which an overflow occurs in one of the first two operations, but the third or fourth operation compensates for the overflow. In these cases the overflow depends on the order of the operands. There will be no overflow if the source operands are exchanged. These two cases of complicated overflow are: • R1 + A2 \* B1 causes an overflow. (R1 + A2 \* B1) + A1 \* B2 compensates for the overflow. • R0 - A2 \* B2 causes an overflow. (R0 - A2 \* B2) + A1 \* B1 compensates for the overflow. The following section presents 4 examples of these cases: 6.0 EXAMPLES OF COMPLICATED OVERFLOW Example 1: Intermediate overflow on R1 + A2 \* B1 when R1 + A2 \* B1 + A1 \* B2 does not cause an overflow. This assumes that A2 \* B1 is positive and A1 \* B2 is negative. If operands A and B were exchanged, there would not have been an overflow. rl = 6000000 # a2 \* bl = 31000000# rl + a2 \* bl = 91000000  $\rightarrow$  overflow # al \* b2 = c000ffff # rl + a2 \* bl + al \* b2 = 5100ffff  $\rightarrow$  no overflow # ovf9: movd \$h' 6000000, rl \$h' 70007fff, r2 movd movd \$h' 80017000, r3 cmacd r2, r3 Here's what happens when the operation reaches the CMACD. Note that A1 and B1 are in italics, while A2 and B2 are not. srcl src2 = 100000000000001*011100000000000* a2 \* bl rl  $\rightarrow$  carry bit = 1  $\rightarrow$  carry bit = 0  $\rightarrow$  Overflow al \* b2 = 110000000000000011111111111111 final result = rl + a2 \* bl + a1 \* b2final result = 010100010000000111111111111111 The final result is correct although there was an intermediate overflow. Now we check the same instruction when we exchange the order of the operands. Note that exchanging the operands prevents overflow (A1 and B1 are still in italics). srcl = 1000000000000010111000000000000 src2 a2 \* bl = 1100000000000001111111111111111 rl rl + a2 \* bl = 0010000000000001111111111111  $\rightarrow$  carry bit = 1  $\rightarrow$  carry bit = 1  $\rightarrow$  No Overflow al \* b2 final result = rl + a2 \* bl + a1 \* b2final result = 01010001000000011111111111111 We can see that the result is similar to the previous and no overflow occurred during the instruction operation.

4

```

Example 2: Intermediate overflow on R1 + A2 * B1 when R1 + A2 * B1 + A1 * B2 do not cause an overflow. This

assumes that A2 * B1 is negative and A1 * B2 is positive. If operands A and B were exchanged there wouldn't have been an

overflow.

#

rl

= b0000000

#

a2 * bl

= c000ffff

#

rl + a2 * bl

= 7000ffff \rightarrow overflow

al * b2

= 10000000

#

rl + a2 * bl + al * b2 = 8000ffff \rightarrow no overflow

#

ovfl0: movd $h' b0000000, rl

movd $h' 7fff4000, r2

movd $h' 40008001, r3

cmacd r2, r3

Example 3: Intermediate overflow on R0 - A2 * B2 when R0 - A2 * B2 + A1 * B1 do not overflow. This assumes that

A2 * B2 is negative and A1 * B1 is negative. If operands A and B were exchanged there wouldn't have been an overflow.

= 6000000

r0

#

a2 * b2

#

= c000ffff

r0 - a2 * b2

#

= 9fff0001 \rightarrow overflow

al * bl

#

= c000ffff

r0 - a2 * b2 + al * bl = 60000000 \rightarrow no overflow

#

ovfll: movd $h' 6000000, r0

movd $h' 7fff8001, r2

movd $h' 80017fff, r3

cmacd r2, r3

Example 4: Intermediate overflow on R0 - A2 * B2 when R0 - A2 * B2 + A1 * B1 do not overflow. This assumes that

A2 * B2 is positive and A1 * B1 is positive. If operands A and B were exchanged there wouldn't have been an overflow.

= b0000000

r0

#

a2 * b2

= 3fff0001

#

r0 - a2 * b2

= 7000ffff \rightarrow overflow

#

#

al * bl

= 10000000

r0 - a2 * b2 + al * b1 = 8000ffff \rightarrow no overflow

#

ovfl2: movd $h' b0000000, r0

movd $h' 7fffc000, r2

movd $h' 7fffc000, r3

cmacd r2, r3

```

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.