mai 2 .

## PRELIMINARY

67 ns

200 ns

April 1991

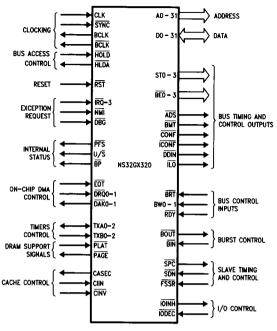

## NS32GX320-20/NS32GX320-25/NS32GX320-30 High-Performance 32-Bit Integrated System Processor

## General Description

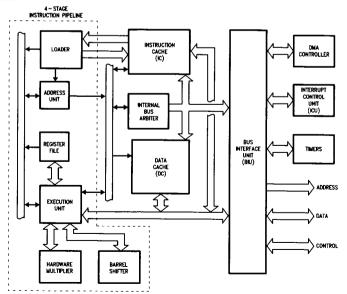

The NS32GX320 is a highly-integrated high-performance member of the Series 32000/EPTM family of National's Embedded System Processors™ specifically designed for computation-intensive, embedded applications. It is software compatible with the previous microprocessors in the family while providing new features to better support Graphics and Digital Signal Processing.

The NS32GX320 CPU core incorporates a 4-stage instruction pipeline, on-chip instruction and data caches, a barrel shifter and a hardware multiplier unit. The internal organization allows a high degree of parallism in executing instruc-

Integrated on the same chip with the CPU are also a 2-channel DMA controller, a 15-level interrupt control unit (ICU) and three 16-bit timers. These make the device extremely attractive for those cost-sensitive applications where a high level of integration is required.

The system interface is also optimized to support applications spanning a wide range, from low-cost, real-time controllers to highly sophisticated, embedded systems.

The NS32GX320 integrates more than 390,000 transistors fabricated in sub-micron, double-metal CMOS technology. The advanced technology and mainframe—like design allow the device to achieve peak performance of 15 million instructions per second.

### **Features**

- 32-bit architecture and implementation

- 4-GByte uniform addressing space

- 512-Byte on-chip instruction cache

- 1024-Byte on-chip data cache

- Verv Efficient DSP Support

- 32-bit Add

- 16x16-to-32-bit Multiply

- Multiply and Accumulate Double

- 367 ns - Complex Multiply and Accumulate 400 ns

- High-performance/low-cost bus

- Separate 32-bit address and data lines

- Burst mode memory accessing

- Dvnamic bus sizing

- Support for page-mode and static-column DRAMs

- Idle states for slow peripherals

- On-chip 15-level Interrupt Control Unit

- On-chip 2-channel DMA Controller (30 Mbytes/sec)

- Three on-chip Timers

- Floating-point support via the NS32381

- Software compatible with the Series 32000 architecture

- Double-metal CMOS technology

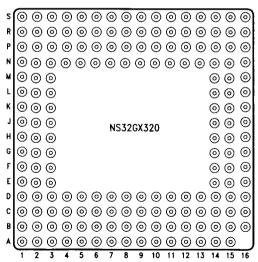

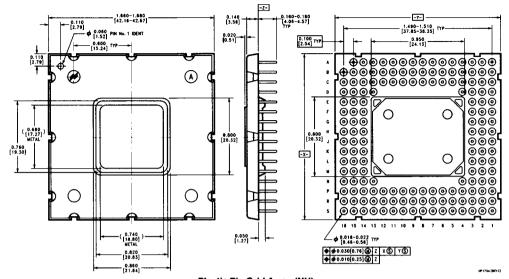

- 175-Pin Plastic Pin Grid Array (PGA) package

## **Block Diagram**

TL/EE/10564-1

FIGURE 1

Series 32000® and TRI-STATE® are registered trademarks of National Semiconductor Corporation Embedded System Processor™ is a trademark of National Semiconductor Corporation.

### **Table of Contents**

#### 1.0 PRODUCT INTRODUCTION

#### 2.0 ARCHITECTURAL DESCRIPTION

- 2.1 Register Set

- 2.1.1 General Purpose Registers

- 2.1.2 Address Registers

- 2.1.3 Processor Status Register

- 2.1.4 Configuration Register

- 2.1.5 Debug Registers

- 2.1.6 DMA Controller Registers

- 2.1.7 Interrupt Control Unit (ICU) Registers

- 2.1.8 Timers Registers

- 2.2 Memory Organization

- 2.2.1 Address Mapping

- 2.3 Modular Software Support

- 2.4 Instruction Set

- 2.4.1 General Instruction Format

- 2.4.2 Addressing Modes

- 2.4.3 Instruction Set Summary

#### 3.0 FUNCTIONAL DESCRIPTION

- 3.1 Instruction Execution

- 3.1.1 Operating States

- 3.1.2 Instruction Endings

- 3.1.2.1 Completed Instructions

- 3.1.2.2 Suspended Instructions

- 3.1.2.3 Terminated Instructions

- 3.1.2.4 Partially Completed Instructions

- 3.1.3 Instruction Pipeline

- 3.1.3.1 Branch Prediction

- 3.1.3.2 Memory Mapped I/O

- 3.1.3.3 Serializing Operations

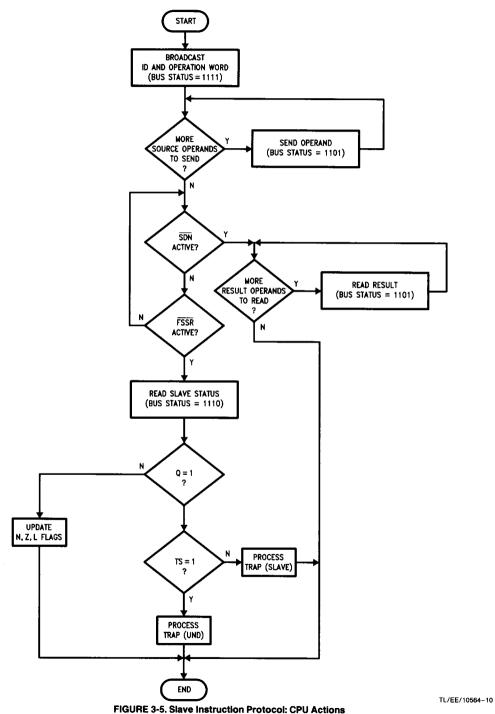

- 3.1.4 Slave Processor Instructions

- 3.1.4.1 Slave Instruction Protocol

- 3.1.4.2 Floating-Point Instructions

- 3.1.4.3 Custom Slave Instructions

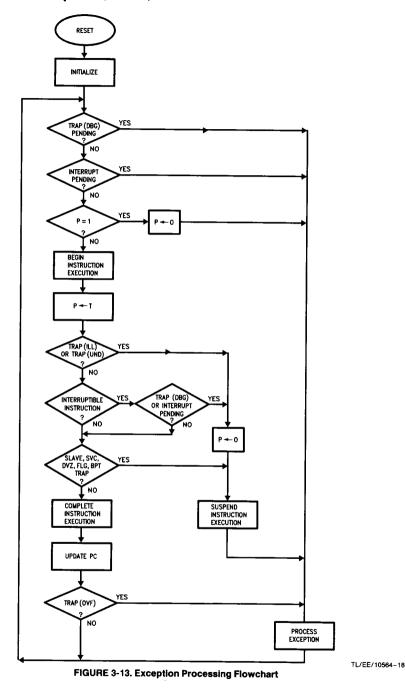

- 3.2 Exception Processing

- 3.2.1 Exception Acknowledge Sequence

- 3.2.2 Returning from an Exception Service Procedure

- 3.2.3 Maskable Interrupts

- 3.2.4 Non-Maskable Interrupt

- 3.2.5 Traps

- 3.2.6 Priority Among Exceptions

- 3.2.7 Exception Acknowledge Sequences: Detailed Flow

- 3.2.7.1 Maskable/Non-Maskable Interrupt Sequence

- 3.2.7.2 SLAVE/ILL/SVC/DVZ/FLG/BPT/UND Trap Sequence

- 3.2.7.3 Trace Trap Sequence

- 3.2.7.4 Integer-Overflow Trap Sequence

- 3.2.7.5 Debug Trap Sequence

- 3.3 Debugging Support

- 3.3.1 Instruction Tracing

- 3.3.2 Debug Trap Capability

- 3.4 On-Chip Caches

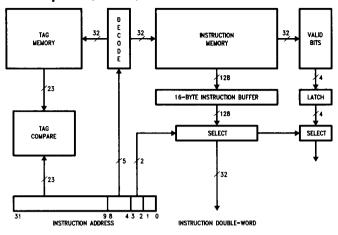

- 3.4.1 Instruction Cache (IC)

- 3.4.2 Data Cache (DC)

- 3.4.3 Cache Coherence Support

- 3.5 On-Chip Peripherals

- 3.5.1 DMA Controller

- 3.5.1.1 Flyby (Direct) Transfers

- 3.5.1.2 Indirect (Memory-to-Memory) Transfers

- 3.5.1.3 Single Transfer Operation

- 3.5.1.4 Double Buffer Operation

- 3.5.1.5 Auto Initialize Operation

- 3.5.1.6 Bus Arbitration

- 3.5.2 Interrupt Control Unit (ICU)

- 3.5.2.1 Interrupt-Acknowledge Processing

- 3.5.2.2 End-of-Interrupt Processing

- 3.5.3 Timers

- 3.5.3.1 Processor Independent Mode (Mode 1)

- 3.5.3.2 External Event Counter Mode (Mode 2)

- 3.5.3.3 Input Capture Mode (Mode 3)

- 3.6 System Interface

- 3.6.1 Power and Grounding

- 3.6.2 Clocking

- 3.6.3 Resetting

- 3.6.4 Bus Cycles

- 3.6.4.1 Bus Status

- 3.6.4.2 Basic Read and Write Cycles

- 3.6.4.3 Burst Cycles

- 3.6.4.4 Cycle Extension

- 3.6.4.5 Interlocked Bus Cycles

- 3.6.4.6 Special Bus Cycles

- 3.6.4.7 DMA Controller Bus Cycles

- 3.6.4.8 Slave Processor Bus Cycles

### Table of Contents (Continued)

#### 3.0 FUNCTIONAL DESCRIPTION (Continued)

3.6.5 Bus Retry

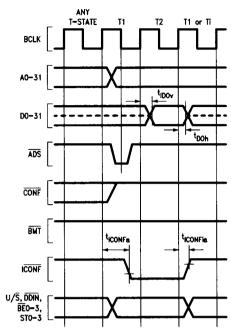

3.6.6 Dynamic Bus Configuration

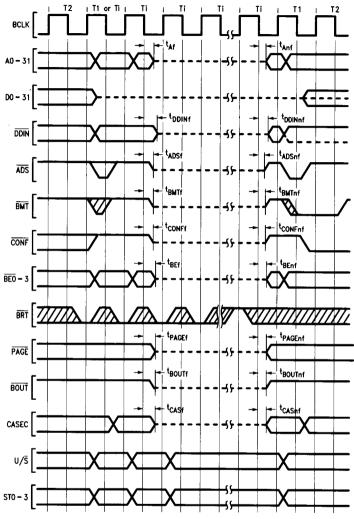

3.6.6.1 Instruction Fetch Sequences

3.6.6.2 Data Read Sequences

3.6.6.3 Data Write Sequences

3.6.7 Bus Access Control

3.6.8 Interfacing Memory-Mapped I/O Devices

3.6.9 Interrupt and Debug Trap Requests

3.6.10 Internal Status

3.6.11 Page-Mode and Static-Column DRAM Support

#### 4.0 DEVICE SPECIFICATIONS

4.1 Pin Descriptions

4.1.1 Supplies

4.1.2 Input Signals

4.1.3 Output Signals

4.1.4 Input/Output Signals

4.2 Absolute Maximum Ratings

4.3 Electrical Characteristics

4.4 Switching Characteristics

#### 4.0 DEVICE SPECIFICATIONS (Continued)

4.4.1 Definitions

4.4.2 Timing Tables

4.4.2.1 Output Signals: Internal Propagation Delays

4.4.2.2 Input Signal Requirements

4.4.3 Timing Diagrams

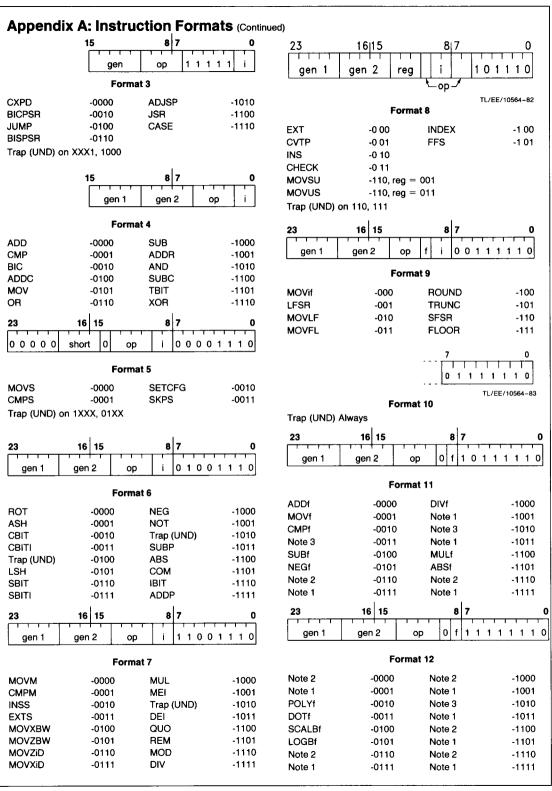

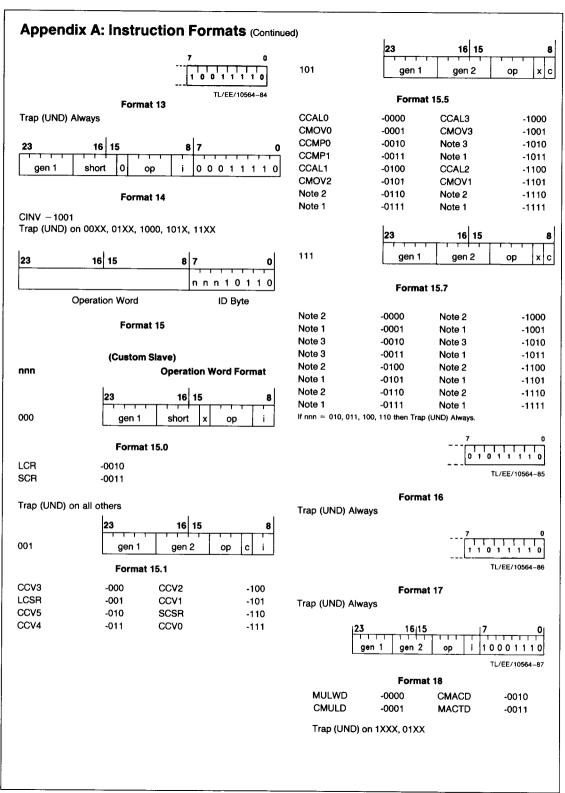

#### **APPENDIX A: INSTRUCTION FORMATS**

#### **B: COMPATIBILITY ISSUES**

**B.1 Restrictions on Compatibility**

**B.2 Architecture Extensions**

**B.3 Integer-Overflow Trap**

**B.4 Self-Modifying Code**

B.5 Memory-Mapped I/O

#### C: INSTRUCTION SET EXTENSIONS

C.1 Processor Service Instructions

C.2 Instruction Definitions

#### **D: INSTRUCTION EXECUTION TIMES**

D.1 Internal Organization and Instruction Execution

D.2 Basic Execution Times

D.2.1 Loader Timing

D.2.2 Address Unit Timing

D.2.3 Execution Unit Timing

**D.3 Instruction Dependencies**

D.3.1 Data Dependencies

D.3.1.1 Register Interlocks

D.3.1.2 Memory Interlocks

D.3.2 Control Dependencies

D.4 Storage Delays

D.4.1 Instruction Cache Misses

D.4.2 Data Cache Misses

D.4.3 Instruction and Operand Alignment

D.5 Execution Time Calculations

D.5.1 Definitions

D.5.2 Notes on Table Use

D.5.3 Teff Evaluation

D.5.4 Instruction Timing Example

D.5.5 Execution Timing Tables

D.5.5.1 Basic and Memory

Management Instructions

D.5.5.2 Floating-Point Instructions,

CPU Portion

## **List of Illustrations**

| CPU Block Diagram                                                                 | 1      |

|-----------------------------------------------------------------------------------|--------|

| NS32GX320 Internal Registers                                                      | 2-1    |

| Processor Status Register (PSR)                                                   | 2-2    |

| Configuration Register (CFG)                                                      | 2-3    |

| Debug Condition Register (DCR)                                                    | 2-4    |

| Debug Status Register (DSR)                                                       | 2-5    |

| DMA Controller Registers Address Map                                              | 2-6    |

| DMA Status Register (STAT)                                                        | 2-7    |

| DMA Interrupt Mask Register (IMSK)                                                | 2-8    |

| DMA Mode Control Register (MODE)                                                  | 2-9    |

| Channel Control Register (CNTL)                                                   | . 2-10 |

| ICU Registers Address Map                                                         | . 2-11 |

| Interrupt Vector Register (IVCT)                                                  | . 2-12 |

| Timer Registers Address Map                                                       |        |

| Timer Control Register (TCNTL)                                                    | . 2-14 |

| NS32GX320 Address Mapping                                                         | 2-15   |

| NS32GX320 Run-Time Environment                                                    | 2-16   |

| General Instruction Format                                                        | 2-17   |

| Index Byte Format                                                                 | 2-18   |

| Displacement Encodings                                                            |        |

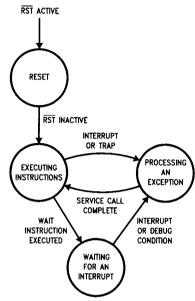

| Operating States                                                                  |        |

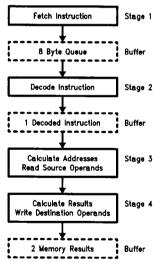

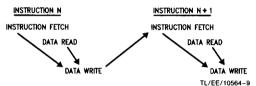

| NS32GX320 Internal Instruction Pipeline                                           | 3-2    |

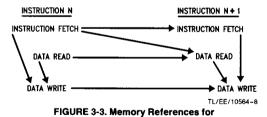

| Memory References for Consecutive Instructions                                    | . 3-3  |

| Memory References after Serialization                                             |        |

| Slave Instruction Protocol: CPU Actions                                           |        |

| ID and Operation Word                                                             |        |

| Slave Processor Status Word                                                       | 3-7    |

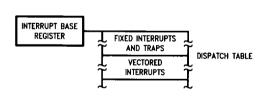

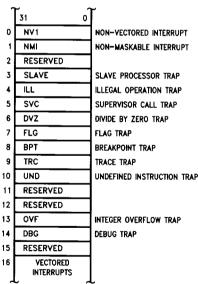

| Interrupt Dispatch Table                                                          | 3-8    |

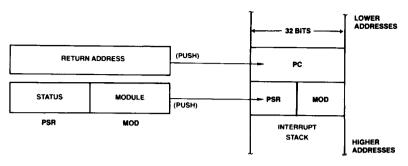

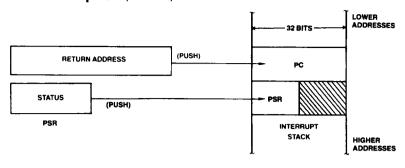

| Exception Acknowledge Sequence: Direct-Exception Mode Disabled                    |        |

| Exception Acknowledge Sequence: Direct-Exception Mode Enabled                     | 3-10   |

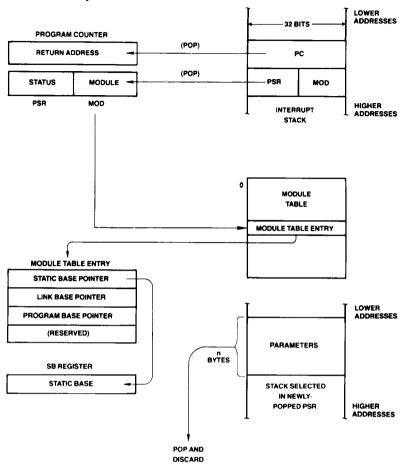

| Return From Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled         |        |

| Return From Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled     |        |

| Exception Processing Flowchart                                                    |        |

| Service Sequence                                                                  | 3-14   |

| Instruction Cache Structure                                                       | 3-15   |

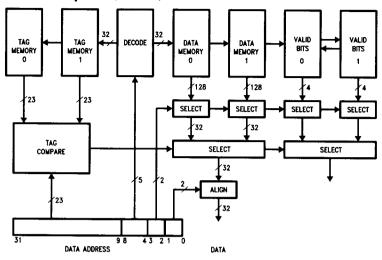

| Data Cache Structure                                                              | 3-16   |

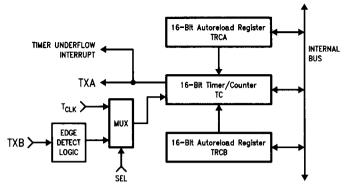

| Timer Block Diagram for the Processor Independent and External Event Counter Mode | 3-17   |

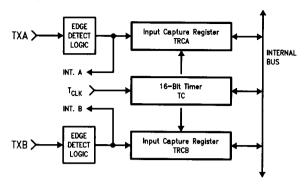

| Timer Block Diagram for the Input Capture Mode                                    |        |

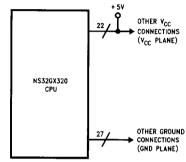

| Power and Ground Connections                                                      |        |

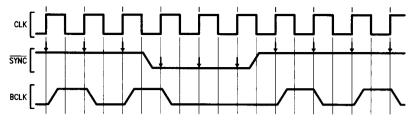

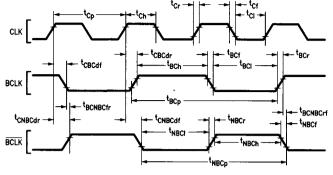

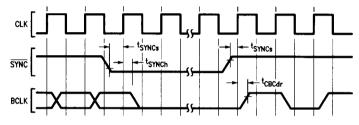

| Bus Clock Synchronization                                                         |        |

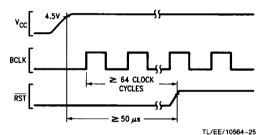

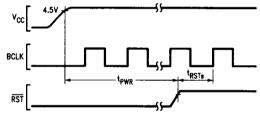

| Power-On Reset Requirements                                                       |        |

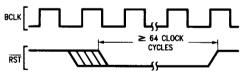

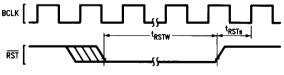

| General Reset Timing                                                              |        |

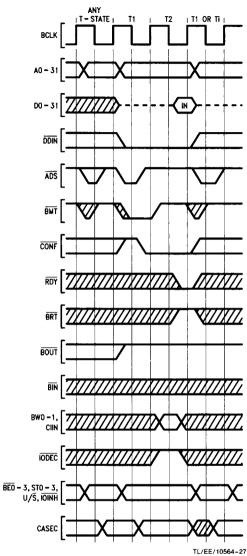

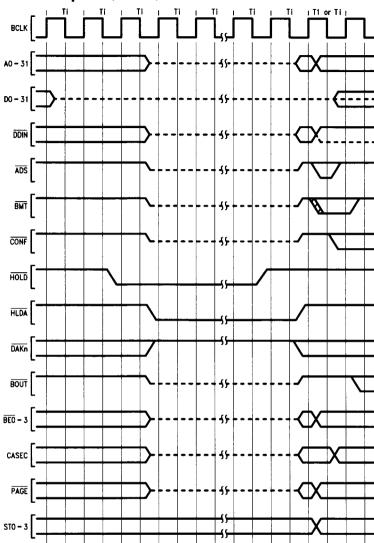

| Basic Read Cycle                                                                  |        |

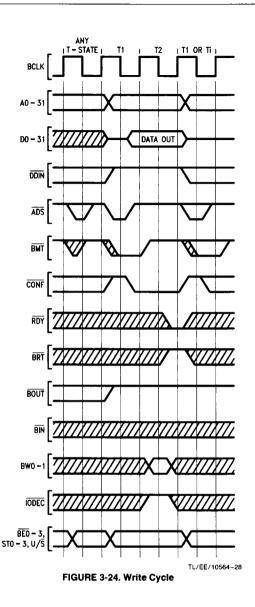

| Write Cycle                                                                       |        |

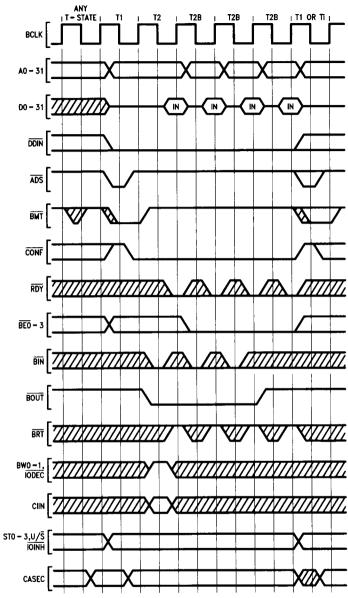

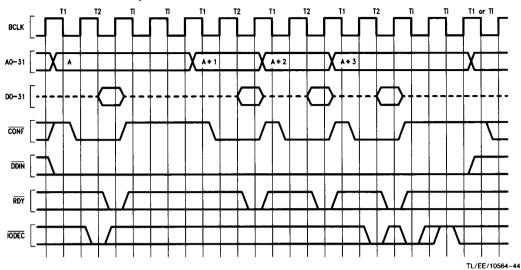

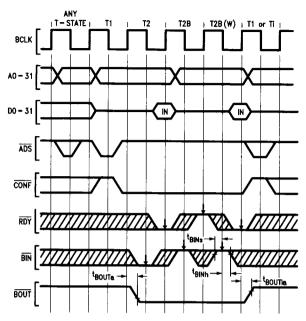

| Burst Read cycles                                                                 |        |

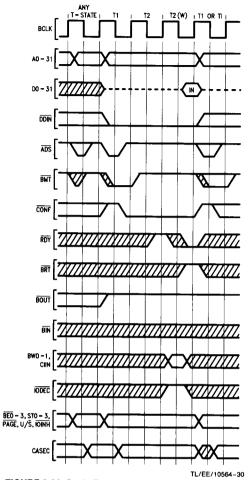

| Cycle Extension of a Basic Read Cycle                                             | 3-25   |

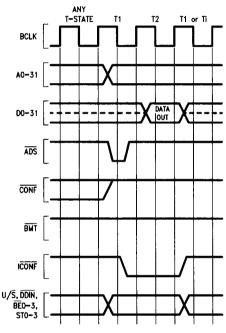

| Type-2 Special Bus Cycle                                                          |        |

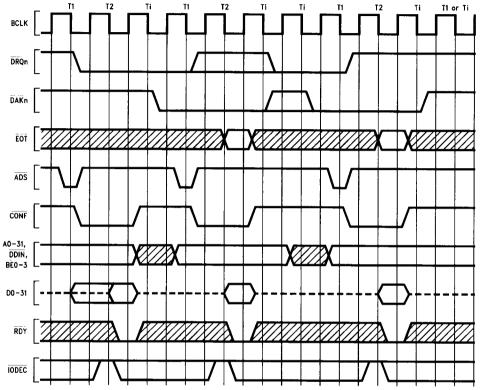

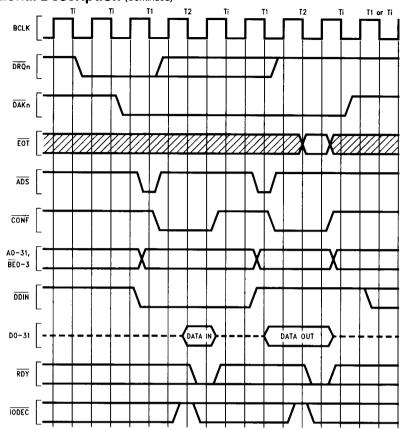

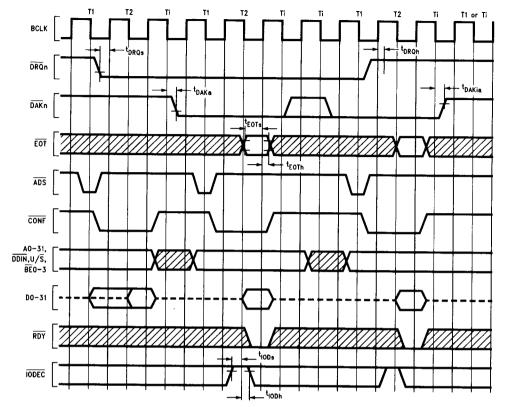

| Flyby DMA Transfer Cycles (Bus Initially Not Idle)                                | 3 20   |

| Indirect (Memory-to-Memory) DMA Transfer Cycles (Bus Initially Idle)              | 3_20   |

|                                                                                   |        |

## List of Illustrations (Continued)

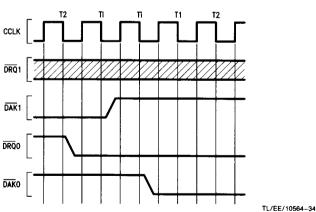

| Successive DMA Transfers on Different Channels          | 3-30          |

|---------------------------------------------------------|---------------|

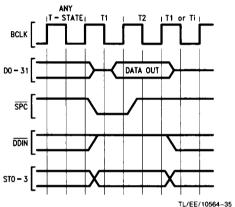

| Slave Processor Write Cycle                             | 3-31          |

| Slave Processor Read Cycle                              | 3-32          |

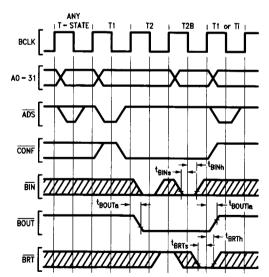

| Bus Retry During a Basic Read Cycle                     | 3-33          |

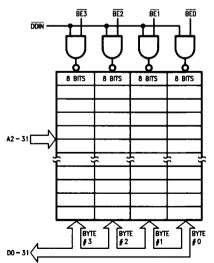

| Basic Interface for 32-Bit Memories                     | 3-34          |

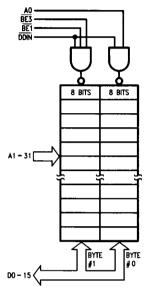

| Basic Interface for 16-Bit Memories                     | 3-35          |

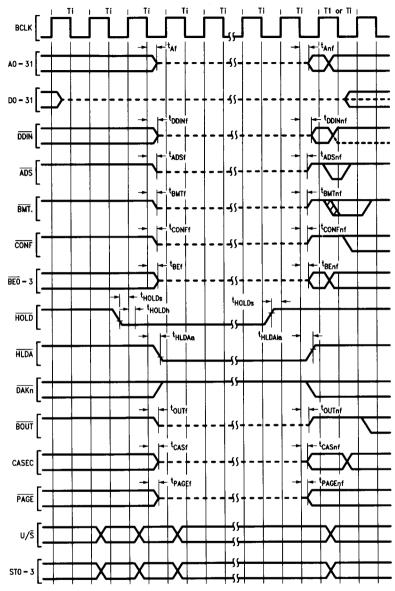

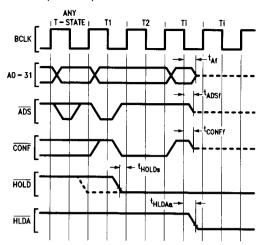

| Hold Acknowledge: (Bus Initially Idle)                  | 3-36          |

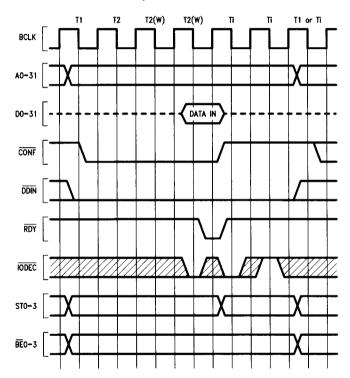

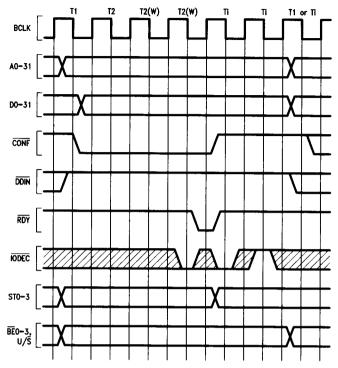

| Read Cycle from Memory-Mapped I/O Device                | 3-37          |

| Write Cycle to Memory-Mapped I/O Device                 | 3 <b>-</b> 38 |

| Multi-Cycle Read from an 8-Bit Memory-Mapped I/O Device | 3-39          |

| Typical I/O Device Interface                            | 3-40          |

| Interrupt Request Encoding Logic                        |               |

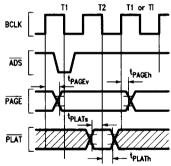

| PAGE and PLAT Signals Timing                            | 3-42          |

| PAGE Signal Generation Logic                            | 3-43          |

| NS32GX320 Interface Signals                             | 4-1           |

| 175-Pin Plastic PGA Package                             | 4-2           |

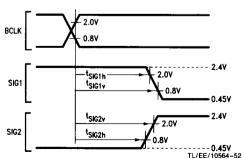

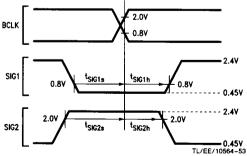

| Output Signals Specification Standard                   | 4-3           |

| Input Signals Specification Standard                    | 4-4           |

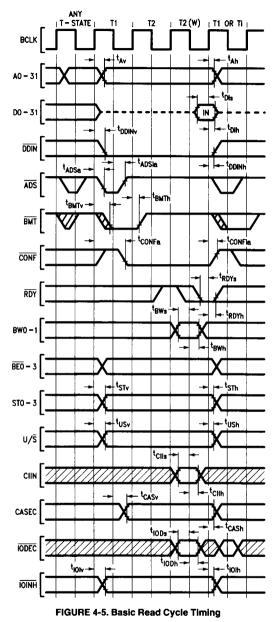

| Basic Read Cycle Timing                                 | 4-5           |

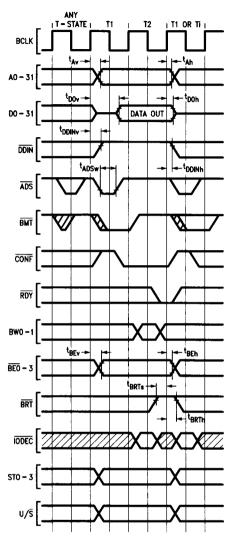

| Write Cycle Timing                                      | 4-6           |

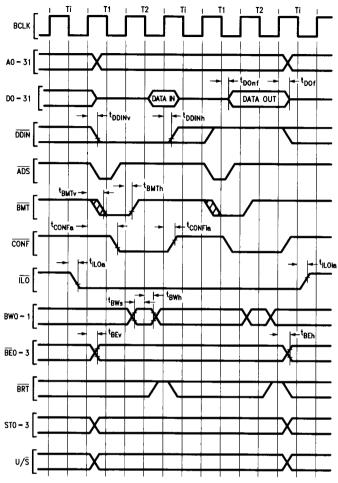

| Interlocked Read and Write Cycles                       | 4-7           |

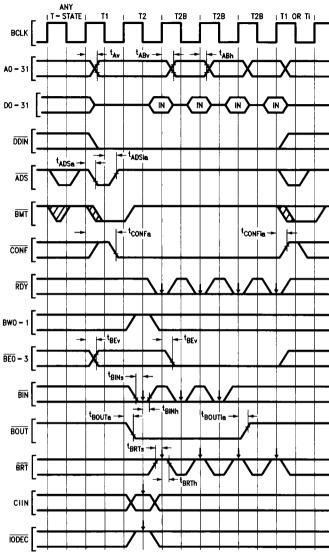

| Burst Read Cycles                                       | 4-8           |

| External Termination of Burst Cycles                    | 4-9           |

| Bus Retry During Burst Cycles                           | 4-10          |

| Extended Retry Timing                                   | 4-11          |

| Type-2 Special Bus Cycle                                | 4-12          |

| Flyby DMA Transfer Cycles (Bus Initially Not Idle)      | 4-13          |

| HOLD Timing (Bus Initially Idle)                        | 4-14          |

| HOLD Acknowledge Timing (Bus Initially Not Idle)        | 4-15          |

| Slave Processor Read Timing                             |               |

| Slave Processor Write Timing                            | 4-17          |

| Slave Processor Done                                    | 4-18          |

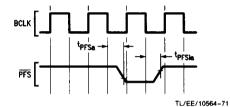

| FSSR Signal Timing                                      | 4-19          |

| IRO-3 and NMI Signals Sampling                          | 4-20          |

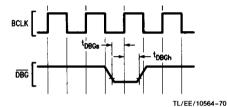

| Debug Trap Request                                      | 4-21          |

| PFS Signal Timing                                       | 4-22          |

| PAGE and PLAT Signals Timing                            | 4-23          |

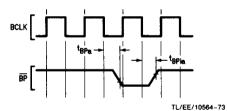

| Break Point Signal Timing                               | 4-24          |

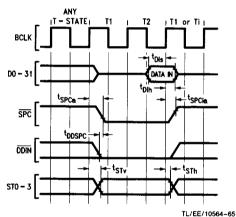

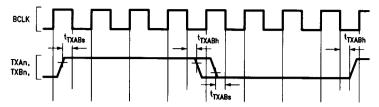

| TXAn and TXBn Input Timing                              | 4-25          |

| TXAn Output Timing                                      | 4-26          |

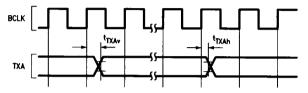

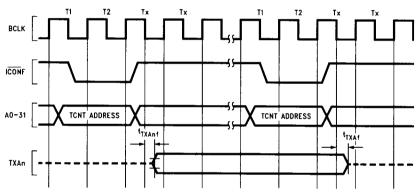

| TXAn Float/Non-Float Timing                             | 4-27          |

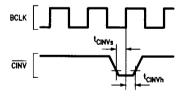

| Cache Invalidation Timing                               | 4-28          |

| Clock Waveforms                                         | 4-29          |

| Bus Clock Synchronization                               |               |

| Power-On Reset                                          |               |

| Non-Power-On Reset                                      |               |

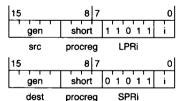

| LPRi/SPRi Instruction Formats                           |               |

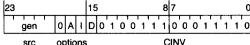

| CINV Instruction Format                                 | C-2           |

|                                                         |               |

## List of Illustrations (Continued)

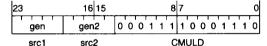

| MULWD Instruction Format                                             |      |

|----------------------------------------------------------------------|------|

| CMULD Instruction Format                                             |      |

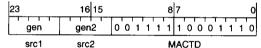

| CMACD Instruction Format                                             |      |

| MACTD Instruction Format                                             | C-6  |

|                                                                      |      |

| List of Tables                                                       |      |

| NS32GX320 Addressing Modes                                           | 2-1  |

| NS32GX320 Instruction Set Summary                                    | 2-2  |

| Floating-Point Instruction Protocol                                  |      |

| Custom Slave Instruction Protocols                                   | 3-2  |

| Summary of Exception Processing                                      | 3-3  |

| Maximum Number of Back-to-Back DMA Transfers                         | 3-4  |

| Interrupt Sources and Priority Levels                                | 3-5  |

| Timer Modes                                                          | 3-6  |

| Interrupt Sequences                                                  | 3-7  |

| Cacheable/Non-Cacheable Instruction Fetches from a 32-Bit Bus        | 3-8  |

| Cacheable/Non-Cacheable Instruction Fetches from a 16-Bit Bus        | 3-9  |

| Cacheable/Non-Cacheable Instruction Fetches from an 8-Bit Bus        |      |

| Cacheable/Non-Cacheable Data Reads from a 32-Bit Bus                 | 3-11 |

| Cacheable/Non-Cacheable Data Reads from a 16-Bit Bus                 | 3-12 |

| Cacheable/Non-Cacheable Data Reads from an 8-Bit Bus                 |      |

| Data Writes to a 32-Bit Bus                                          | 3-14 |

| Data Writes to a 16-Bit Bus                                          | 3-15 |

| Data Writes to an 8-Bit Bus                                          | 3-16 |

| LPRi/SPRi New 'Short' Field Encodings                                |      |

| Additional Address Unit Processing Time for Complex Addressing Modes | D-1  |

|                                                                      |      |

### 1.0 Product Introduction

The NS32GX320 is an extremely sophisticated microprocessor in the Series 32000/EP family with a full 32-bit architecture and implementation optimized for high-performance embedded applications.

By employing a number of mainframe-like features, the device can deliver 15 MIPS peak performance with no wait states at a frequency of 30 MHz.

In addition to the very powerful CPU core, the NS32GX320 integrates on the same chip a number of peripherals, namely: a 2-channel DMA Controller, a 15-level Interrupt Control Unit (ICU) and three 16-bit timers.

The NS32GX320 is software compatible with the other CPUs of the Series 32000 architecture. The main features of the Series 32000 architecture and particularly the NS32GX320, are described briefly below.

Powerful Addressing Modes. Nine addressing modes available to all instructions are included to access data structures efficiently.

Data Types. The architecture provides for numerous data types, such as byte, word, doubleword, and BCD, which may be arranged into a wide variety of data structures.

Symmetric Instruction Set. While avoiding special case instructions that compilers can't use, the Series 32000 architecture incorporates powerful instructions for control operations, such as array indexing and external procedure calls, which save considerable space and time for compiled code

**Memory-to-Memory Operations.** The Series 32000 CPUs represent two-address machines. This means that each operand can be referenced by any one of the addressing modes provided.

This powerful memory-to-memory architecture permits memory locations to be treated as registers for all useful operations. This is important for temporary operands as well as for context switching.

Large, Uniform Addressing. The NS32GX320 has 32-bit address pointers that can address up to 4 gigabytes without requiring any segmentation.

Modular Software Support. Any software package for the Series 32000 architecture can be developed independent of all other packages, without regard to individual addressing. In addition, ROM code is totally relocatable and easy to access, which allows a significant reduction in hardware and software costs.

Software Processor Concept. The Series 32000 architecture allows future expansions of the instruction set that can be executed by special slave processors, acting as extensions to the CPU. This concept of slave processors is unique to the Series 32000 architecture. It allows software compatibility even for future components because the slave hardware is transparent to the software. With future advances in semiconductor technology, the slaves can be physically integrated on the CPU chip itself.

To summarize, the architectural features cited above provide three primary performance advantages and characteristics:

- High-level language support

- · Easy future growth path

- · Application flexibility

### 2.0 Architectural Description

#### 2.1 REGISTER SET

The NS32GX320 has 54 internal registers. 21 of them belong to the CPU portion of the device and are addressed either implicitly by specific instructions or through the register addressing mode. The other 33 control the operation of the on-chip peripherals, and are memory mapped. *Figure 2-1* shows the NS32GX320 internal registers.

#### 2.1.1 General Purpose Registers

There are eight registers (R0-R7) used for satisfying the high speed general storage requirements, such as holding temporary variables and addresses. The general purpose registers are free for any use by the programmer. They are 32 bits in length. If a general purpose register is specified for an operand that is eight or 16 bits long, only the low part of the register is used; the high part is not referenced or modified

#### 2.1.2 Address Registers

The seven address registers are used by the CPU to implement specific address functions. A description of them follows

PC—Program Counter. The PC register is a pointer to the first byte of the instruction currently being executed. The PC is used to reference memory in the program section.

SP0, SP1—Stack Pointers. The SP0 register points to the lowest address of the last item stored on the INTERRUPT STACK. This stack is normally used only by the operating system. It is used primarily for storing temporary data, and holding return information for operating system subroutines and interrupt and trap service routines. The SP1 register points to the lowest address of the last item stored on the USER STACK. This stack is used by normal user programs to hold temporary data and subroutine return information.

When a reference is made to the selected Stack Pointer (see PSR S-bit), the terms 'SP Register' or 'SP' are used. SP refers to either SP0 or SP1, depending on the setting of the S bit in the PSR register. If the S bit in the PSR is 0, SP refers to SP0. If the S bit in the PSR is 1 then SP refers to SP1.

The NS32GX320 also allows the SP1 register to be directly loaded and stored using privileged forms of the LPRi and SPRi instructions, regardless of the setting of the PSR S-bit. When SP1 is accessed in this manner, it is referred to as 'USP Register' or simply 'USP'.

Stacks in the Series 32000 architecture grow downward in memory. A Push operation pre-decrements the Stack Pointer by the operand length. A Pop operation post-increments the Stack Pointer by the operand length.

FP—Frame Pointer. The FP register is used by a procedure to access parameters and local variables on the stack. The FP register is set up on procedure entry with the ENTER instruction and restored on procedure termination with the EXIT instruction.

The frame pointer holds the address in memory occupied by the old contents of the frame pointer.

SB—Static Base. The SB register points to the global variables of a software module. This register is used to support relocatable global variables for software modules. The SB register holds the lowest address in memory occupied by the global variables of a module.

#### **CPU Registers**

## General Purpose ← 32 Bits →

R0-R7

#### Address

|         | PC      |  |  |  |  |  |

|---------|---------|--|--|--|--|--|

| SI      | P0, SP1 |  |  |  |  |  |

|         | FP      |  |  |  |  |  |

|         | SB      |  |  |  |  |  |

| INTBASE |         |  |  |  |  |  |

|         | MOD     |  |  |  |  |  |

### **Processor Status**

PSR

#### Debua

| DCR |  |

|-----|--|

| DSR |  |

| CAR |  |

| BPC |  |

#### Configuration

CFG

#### FIGURE 2-1. NS32GX320 Internal Registers

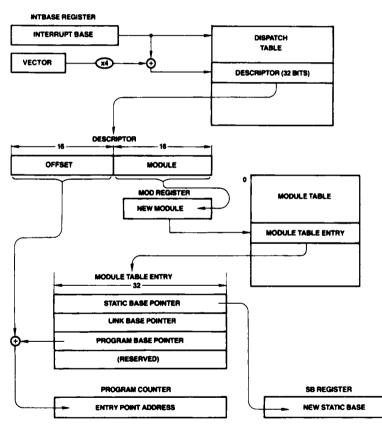

INTBASE—Interrupt Base. The INTBASE register holds the address of the dispatch table for interrupts and traps (Section 3.2.1).

MOD—Module. The MOD register holds the address of the module descriptor of the currently executing software module. The MOD register is 16 bits long, therefore the module table must be contained within the first 64 kbytes of memory.

#### 2.1.3 Processor Status Register

The Processor Status Register (PSR) holds status information for the microprocessor.

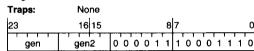

The PSR is sixteen bits long, divided into two eight-bit halves. The low order eight bits are accessible to all programs, but the high order eight bits are accessible only to programs executing in Supervisor Mode.

- C The C bit indicates that a carry or borrow occurred after an addition or subtraction instruction. It can be used with the ADDC and SUBC instructions to perform multiple-precision integer arithmetic calculations. It may have a setting of 0 (no carry or borrow) or 1 (carry or borrow).

- T The T bit causes program tracing. If this bit is set to 1, a TRC trap is executed after every instruction (Section 3.3.1).

#### **Peripherals Registers**

## DMA Controller ← 32 Bits →

| STAT        |  |

|-------------|--|

| IMSK        |  |

| DSTAT       |  |

| ADCA (0, 1) |  |

| ADRA (0, 1) |  |

| ADCB (0, 1) |  |

| ADRB (0, 1) |  |

| BLTC (0, 1) |  |

| BLTR (0, 1) |  |

| MODE (0, 1) |  |

| CNTL (0, 1) |  |

#### Interrupt Control Unit

|     | IVCT |

|-----|------|

| ISI | ₹∨   |

#### Timers

| TC (0, 1, 2)    |

|-----------------|

| TRCA (0, 1, 2)  |

| TRCB (0, 1, 2)  |

| TCNTL (0, 1, 2) |

- L The L bit is altered by comparison instructions. In a comparison instruction the L bit is set to "1" if the second operand is less than the first operand, when both operands are interpreted as unsigned integers. Otherwise, it is set to "0". In Floating-Point comparisons, this bit is always cleared.

- V The V-bit enables generation of a trap (OVF) when an integer arithmetic operation overflows.

Note: The setting of the V-bit affects the execution times of the multiply and arithmetic shift instructions. Refer to Appendix D for details.

- F The F bit is a general condition flag, which is altered by many instructions (e.g., integer arithmetic instructions use it to indicate overflow).

- Z The Z bit is altered by comparison instructions. In a comparison instruction the Z bit is set to "1" if the second operand is equal to the first operand; otherwise it is set to "0".

- N The N bit is altered by comparison instructions. In a comparison instruction the N bit is set to "1" if the second operand is less than the first operand, when both operands are interpreted as signed integers. Otherwise, it is set to "0".

| 15 | <br> |   |   |   | 8 | 7 |   |   |   |   |   | 0 | ار |

|----|------|---|---|---|---|---|---|---|---|---|---|---|----|

|    |      | ı | Р | s | U | N | Z | F | V | L | T | С | 1  |

FIGURE 2-2. Processor Status Register (PSR)

- U If the U bit is "1" no privileged instructions may be executed. If the U bit is "0" then all instructions may be executed. When U = 0 the processor is said to be in Supervisor Mode; when U = 1 the processor is said to be in User Mode. A User Mode program is restricted from executing certain instructions and accessing certain registers which could interfere with the operating system. For example, a User Mode program is prevented from changing the setting of the flag used to indicate its own privilege mode. A Supervisor Mode program is assumed to be a trusted part of the operating system, hence it has no such restrictions.

- S The S bit specifies whether the SP0 register or SP1 register is used as the Stack Pointer. The bit is automatically cleared on interrupts and traps. It may have a setting of 0 (use the SP0 register) or 1 (use the SP1 register).

- P The P bit prevents a TRC trap from occurring more than once for an instruction (Section 3.3.1). It may have a setting of 0 (no trace pending) or 1 (trace pending).

- I If I = 1, then all interrupts will be accepted. If I = 0, only the NMI interrupt is accepted. Trap enables are not affected by this bit.

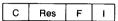

#### 2.1.4 Configuration Register

The Configuration Register (CFG) is 32 bits wide, of which ten bits are implemented. The implemented bits enable various operating modes for the CPU, including vectoring of interrupts, execution of slave instructions, and control of the on-chip caches. In the NS32332 bits 4 through 7 of the CFG register selected between the 16-bit and 32-bit slave protocols and between 512-byte and 4-kbyte page sizes. The NS32GX320 supports only the 32-bit slave protocol and no memory management: consequently these bits are forced to 1.

When the CFG register is loaded using the LPRi instruction, bit 2 and bits 13 through 31 should be set to 0. Bits 4 through 7 are ignored during loading, and are always returned as 1's when CFG is stored via the SPRi instruction. When the SETCFG instruction is executed, the contents of the CFG register bits 0 through 3 are loaded from the instruction's short field, bits 4 through 7 are ignored and bits 8 through 12 are forced to 0. Bit 2 must be set to 0.

The format of the CFG register is shown in *Figure 2-3*. The various control bits are described below.

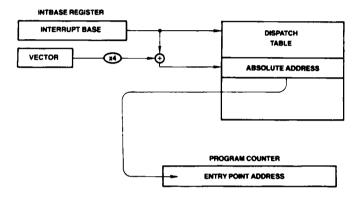

- Interrupt vectoring. This bit controls whether maskable interrupts are handled in nonvectored (I = 0) or vectored (I = 1) mode. Refer to Section 3.2.3 for more information.

- F Floating-point instruction set. This bit indicates whether a floating-point unit (FPU) is present to execute floating-point instructions. If this bit is 0 when the CPU executes a floating-point instruction, a Trap (UND) occurs. If this bit is 1, then the CPU transfers the instruction and any necessary operands to the FPU using the slave-processor protocol described in Section 3.1.4.1.

- C Custom instruction set. This bit indicates whether a custom slave processor is present to execute custom instructions. If this bit is 0 when the CPU executes a custom instruction, a Trap (UND) occurs. If this bit is 1, the CPU transfers the instruction and any necessary operands to the custom slave processor using the slave-processor protocol described in Section 3.1.4.1.

- Direct-Exception mode enable. This bit enables the Direct-Exception mode for processing exceptions. When this mode is selected, the CPU response time to interrupts and other exceptions is significantly improved. Refer to Section 3.2.1 for more information.

- DC Data Cache enable. This bit enables the on-chip Data Cache to be accessed for data reads and writes. Refer to Section 3.4.2 for more information.

- LDC Lock Data Cache. This bit controls whether the contents of the on-chip Data Cache are locked to fixed memory locations (LDC=1), or updated when a data read is missing from the cache (LDC=0).

- IC Instruction Cache enable. This bit enables the onchip Instruction Cache to be accessed for instruction fetches. Refer to Section 3.4.1 for more information.

- LIC Lock Instruction Cache. This bit controls whether the contents of the on-chip Instruction Cache are locked to fixed memory locations (LIC=1), or updated when an instruction fetch is missing from the cache (LIC=0).

| 31       | 12  | _  |     |    | 8  | 7 |   |   |   |   |     |   | 0 |

|----------|-----|----|-----|----|----|---|---|---|---|---|-----|---|---|

| Reserved | LIC | IC | LDC | DC | DE | 1 | 1 | 1 | 1 | С | Res | F | ı |

FIGURE 2-3. Configuration Register (CFG) Bits 13 to 31 are Reserved; Bits 4 to 7 are Forced to 1.

#### 2.1.5 Debug Registers

The NS32GX320 contains 4 registers dedicated for debugging functions.

These registers are accessed using privileged forms of the LPRi and SPRi instructions.

**DCR—Debug Condition Register.** The DCR Register enables detection of debug conditions. The format of the DCR is shown in *Figure 2-4*; the various bits are described below. A debug condition is enabled when the related bit is set to 1.

CBE0 Compare Byte Enable 0; when set, BYTE0 of an aligned double-word is included in the address comparison

CBE1 Compare Byte Enable 1; when set, BYTE1 of an aligned double-word is included in the address comparison

CBE2 Compare Byte Enable 2; when set, BYTE2 of an aligned double-word is included in the address comparison

CBE3 Compare Byte Enable 3; when set, BYTE3 of an aligned double-word is included in the address comparison

CWR Address-compare enable for write references

CRD Address-compare enable for read references

CAE Address-compare enable

TR Enable Trap (DBG) when a debug condition is detected

PCE PC-match enable

UD Enable debug conditions in User-Mode

SD Enable debug conditions in Supervisor Mode

**DEN** Enable debug conditions

The following 2 bits control testing features that can be used during initial system debugging. These features are

unique to the NS32GX320 implementation of the Series 32000 architecture; as such, they may not be supported in future implementations. For normal operation these 2 bits should be set to 0.

SI Single-Instruction mode enable. This bit, when set to 1, inhibits the overlapping of instruction's execution.

BCP Branch Condition Prediction disable. When this bit is 1, the branch prediction mechanism is disabled. See Section 3.1.3.1.

**DSR—Debug Status Register.** The DSR Register indicates debug conditions that have been detected. When the CPU detects an enabled debug condition, it sets the corresponding bit (BC, BEX, BCA) in the DSR to 1. When an address-compare condition is detected, then the RD-bit is loaded to indicate whether a read or write reference was performed. Software must clear all the bits in the DSR when appropriate. The format of the DSR is shown in *Figure 2-5;* the various fields are described below.

RD Indicates whether the last address-compare condition was for a read (RD = 1) or write (RD = 0) reference

BPC PC-match condition detected

BEX External condition detected

BCA Address-compare condition detected

Note: If an address compare is detected for a read and write for the same instruction, the RD bit will remain clear.

CAR—Compare Address Register. The CAR Register contains the address that is compared to operand reference addresses to detect an address-compare condition. The address must be double-word aligned; that is, the two least-significant bits must be 0. The CAR is 32 bits wide.

**BPC—Breakpoint Program Counter.** The BPC Register contains the address that is compared with the PC contents to detect a PC-match condition. The BPC Register is 32 bits wide.

| 15 |          | 8 7  | 0   |     |     |     |      |      |      |      |

|----|----------|------|-----|-----|-----|-----|------|------|------|------|

|    | Reserved |      | CAE | CRD | CWR | Res | CBE3 | CBE2 | CBE1 | CBE0 |

| 31 |          | 24 2 | 23  |     |     |     |      |      |      | 16   |

|    |          |      | DEN | SD  | UD  | PCE | TR   | BCP  | SI   | Res  |

FIGURE 2-4. Debug Condition Register (DCR)

| 31 |     |     | 28  | 27 (     | 0 |

|----|-----|-----|-----|----------|---|

| RD | BPC | BEX | BCA | Reserved | 7 |

FIGURE 2-5. Debug Status Register (DSR)

#### 2.1.6 DMA Controller Registers

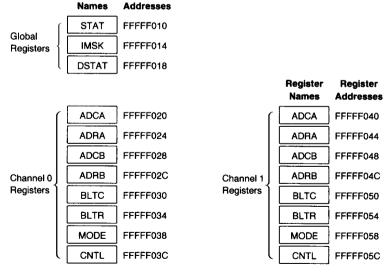

The DMA Controller contains 19 32-bit memory mapped registers that are both readable and writable by software. Three of these registers are common to both channels and are used to report various conditions as well as selectively enable or disable interrupt generation corresponding to each condition. The other 16 registers are divided into two sets of eight, with each set associated to one channel.

All of the registers appear as memory locations, and must be accessed by specifying an operand length of 32 bits. Accesses specifying a length other than 32 bits may cause unpredictable results. The registers DSTAT, ADCA, ADCB, BLTC and MODE must not be written into while the associated channel is enabled. Upon reset, the registers STAT, IMSK, BLTC, BLTR, MODE and CNTL are cleared. Figure 2-6 shows the address map of the DMA registers.

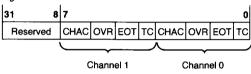

**STAT—Status Register.** This register contains status information for the two DMA channels. Its format is shown in *Figure 2-7*.

#### FIGURE 2-7. DMA Status Register (STAT)

TC Terminal Count; when set to 1, indicates that the transfer was completed by a terminal count condition (BLTC Register reached zero).

Register

Register

EOT External End Of Transfer. This bit is set to 1 when the transfer is externally terminated by the assertion of the EOT signal.

OVR Channel Overrun. Used only with double-buffered transfers. OVR is set to 1 when the present transfer is completed (BLTC = 0), but the parameters for the next transfer (addresses and block length) are not valid.

CHAC Channel Active. When set to 1, indicates that the channel is active (CHEN bit in register CNTL is 1 and BLTC > 0).

The TC, EOT and OVR bits are sticky. This means that, once set by the occurrence of the specific condition, they will remain set until explicitly cleared by software. These bits can be individually cleared by writing a value into the STAT register with the bit positions to be cleared set to 1. The CHAC bit continuously reflects the active or inactive status of the channel, and therefore, it is READ only.

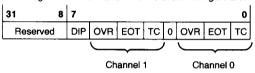

**IMSK—Interrupt Mask.** This register is used to enable or disable interrupts for various conditions recorded in the STAT register. The format of IMSK is shown in *Figure 2-8*.

FIGURE 2-8. DMA Interrupt Mask Register (IMSK)

FIGURE 2-6. DMA Controller Registers Address Map

The DIP bit selects the DMA Interrupt Priority level in the Interrupt Control Unit. When a DIP is 0, the priority level is 6; when DIP is 1, the priority level is 14. Bits 0-2 and 4-6 are the Interrupt Mask Bits. An interrupt is enabled when the corresponding mask bit is set to 1.

DSTAT—DMA Debug Status Register. DSTAT is an image of the STAT register and provides an alternate means for accessing STAT. Writing a value into DSTAT stores the value itself into the STAT register, as opposed to only clearing bits as when writing directly into STAT. Setting a bit into DSTAT affects the associated interrupt as well as the CHEN bit in the CNTL register, according to the respective mask bit in IMSK.

ADCA—Device A Address Counter. In Indirect transfer mode, holds the current address of the source data item to be transferred. In Flyby mode, holds the current address of either the source data item or the destination location in the Addressed Device. If the ADA bit in the MODE register is set to 1, ADCA is incremented after each transfer cycle by the number of bytes transferred.

ADRA—Device A Address Register. In Indirect transfer mode, holds the starting address of the next source data block to be transferred. In Flyby mode, holds the starting address of either the source data block or the destination data area in the Addressed Device.

ADCB—Device B Address Counter. In Indirect transfer mode, holds the address of the destination location to receive the data item to be transferred. If the ADB bit in the MODE register is set to 1, ADCB is incremented after each transfer cycle by the number of bytes transferred. ADCB is not used in Flyby mode.

**ADRB—Device B Address Register.** In Indirect transfer mode, holds the starting address of the next destination data area to receive the block of data. ADRB is not used in Flyby mode.

**BLTC—Block Length Counter.** Holds the current number of bytes to be transferred. BLTC is decremented after each transfer cycle by the number of bytes transferred.

**BLTR—Block Length Register.** Holds the number of bytes in the next block to be transferred. Writing a zero value into BLTR while the VLD and CHEN bits in CNTL are both set to 1 may cause unpredictable results.

Note 1: The ADRA, ADRB and BLTR registers are used to store the transfer parameters (i.e., source address, destination address and block length) for the next data block to be transferred, for either auto-initialize or double-buffer modes of operation.

Note 2: The values programmed into ADCA, ADRA, ADCB, ADRB, BLTC and BLTR must be multiples of the smaller of the source and destination bus widths programmed in the mode register.

**MODE—Mode Control Register.** This register is used to specify the channel operating mode. The format of MODE is shown in *Figure 2-9*. Bit 1 and bits 15 through 31 should be set to 0.

OT Operation Type.

OT = 0 → Auto-Initialize Mode Disabled

OT = 1 → Auto-Initialize Mode Enabled

FBY Flyby/Indirect Transfers.

$FBY = 0 \rightarrow Flyby$

FBY = 1 → Indirect (memory-to-memory)

DIR Flyby Transfer Direction. Specifies the direction of transfer between memory and peripheral device during flyby mode.

DIR = 0 → Peripheral Device is Destination

DIR = 1 → Peripheral Device is Source

BWB Device B Bus Width.

BWB =  $00 \rightarrow 8$  Bits

BWB = 01 → 16 Bits

BWB = 10 → 32 Bits

BWB = 11 → Reserved

ADB Device B Address Control. Enables the incrementing of the device B address after each transfer cycle.

ADB = 0 → Address Unchanged

ADB = 1 → Address Incremented

BWA Device A Bus Width.

BWA = 00 → 8 Bits

BWA = 01 → 16 Bits

BWA = 10 → 32 Bits

BWA = 11 → Reserved

ADA Device A Address Control. Enables the incrementing of the device A address after each transfer cycle.

ADA = 0 → Address Unchanged

ADA = 1 → Address Incremented

BLT Block Transfer Length. This 5-bit field is used by the bus fairness mechanism, and specifies the maximum number of bytes that can be transferred before the DMA channel relinquishes the bus. Refer to Section 3.5.6 for details.

**CNTL—Channel Control Register.** CNTL is used to synchronize the channel operation with the programming of the block transfer parameters. The format of CNTL is shown in *Figure 2-10*.

| 31       | 2 1 | 0   |      |

|----------|-----|-----|------|

| Reserved |     | VLD | CHEN |

FIGURE 2-10. Channel Control Register (CNTL)

| 31    | 15  | 14 | 10 | 9   | 8  | 7  | 6   | 5 | 4  | 3   | 2   | 1   | 0  |   |

|-------|-----|----|----|-----|----|----|-----|---|----|-----|-----|-----|----|---|

| Reser | ved | BL | .T | ADA | в۷ | VA | ADB | в | VB | DIR | FBY | Res | ОТ | 1 |

FIGURE 2-9. DMA Mode Control Register (MODE)

CHEN Channel Enable.

CHEN = 0 → Channel Disabled

CHEN = 1 → Channel Enabled

VLD Transfer Parameters Valid. Specifies whether the transfer parameters for the next block to be transferred are valid.

VLD = 0 → Parameters Not Valid

VLD = 1 → Parameters Valid

The CHEN bit is set to 0 in the following cases.

- Upon Reset

- · Software clears it by writing to the CNTL register

- . The EOT bit in STAT is set to 1

- . The OVR bit in STAT is set to 1 and is unmasked

In the last two cases the CHEN bit is forced to 0 and cannot be set to 1 by software unless EOT is cleared and OVR is either cleared or masked by clearing the corresponding bit in IMSK.

#### 2.1.7 Interrupt Control Unit (ICU) Registers

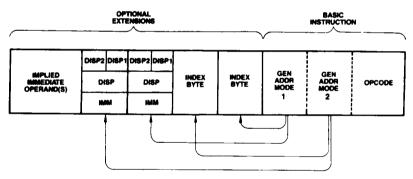

The interrupt control unit contains two memory-mapped registers: IVCT and ISRV. These registers are 8 bits and 16 bits wide respectively, and must be accessed by specifying operand lengths equal to their widths. Specifying different operand lengths may cause unpredictable results. The address map for IVCT and ISRV is shown in Figure 2-11.

| Register<br>Names | Register<br>Addresses |

|-------------------|-----------------------|

| IVCT              | FFFFE00               |

| ISRV              | FFFFE04               |

FIGURE 2-11. ICU Registers Address Map

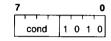

**IVCT—Interrupt Vector Register.** This is a read-only register containing the current interrupt request vector to be used by the CPU in accessing the interrupt dispatch table when the request is acknowledged. Bits 0-3 contain an encoded value representing the interrupt request priority level. The binary value 1111 represents the highest priority level, while the value 0000 indicates that no interrupt request is pending. *Figure 2-12* shows the format of IVCT.

| 7 |   |   |   |   |   |   | 0 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | V | ٧ | ٧ | ٧ |

FIGURE 2-12. Interrupt Vector Register (IVCT)

ISRV Interrupt In-Service Register. ISRV is used by the ICU to keep track of the priority levels of interrupts currently being serviced. A value of 1 in bit position i (where  $1 \le i \le 15$ ), indicates that the i-th priority level is currently in-service. Bit position 0 is always forced to 0. Upon reset the ISRV register is cleared to 0. Note that a zero value in the ISRV register indicates that there are no in-service interrupts.

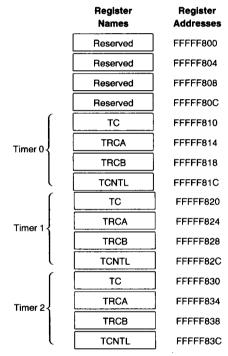

#### 2.1.8 Timers Registers

Each of the three timers in the NS32GX320 is controlled by a set of four registers. These registers are all 16 bits wide, and are memory-mapped. Their address map is shown in *Figure 2-13*. Accesses to the timer registers must specify operand lengths of 16 bits otherwise undefined results may be obtained. Refer to Section 3.5.3 for details on the timer's operation.

FIGURE 2-13. Timer Registers Address Map

**TC—Counter.** TC is a down-counter which, upon underflow, is reloaded with the contents of either TRCA or TRCB for modes 1 and 2, and with all 1's for mode 3.

# TRCA, TRCB—Reload/Capture Registers A and B. These registers hold either the counter reload values or a snapshot of TC.

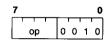

**TCNTL—Timer Control Register.** Used to control the operation of each timer, and to enable timer interrupts. The TCNTL format is shown in *Figure 2-14*.

| 31 12 | 11  | 10  | 9   | 8   | 7 5 | 4   |      |      |      | 0    | ĺ |

|-------|-----|-----|-----|-----|-----|-----|------|------|------|------|---|

| RES   | WIS | WIA | WIB | PRC | тмс | TCS | IPFA | IENA | IPFB | IENB |   |

#### FIGURE 2-14. Timer Control Register (TCNTL)

**IENB** Interrupt Enable Bit B. When set to 1, enables the interrupt from IPFB.

IPFB Interrupt Pending Flag B.

IENA Interrupt Enable Bit A. When set to 1, enables the interrupt from IPFA. If Mode 3 is selected, it enables the interrupt from TCS as well.

IPFA Interrupt Pending Flag A.

TCS Timer Control and Status. In modes 1 or 2, this bit is used to start and stop the timer. The timer starts when TCS is 1. In mode 3, TCS is the underflow interrupt pending flag.

**TMC** Timer Mode Control. This three-bit field selects the timer mode of operation. (See Section 3.5.3.)

PRC Prescaler Control. Used only in modes 1 and 3. PRC controls the frequency of the timer input clock (TCLK). When PRC = 0, TCLK = BCLK/8; when PRC = 1, TCLK = BCLK/4096.

WIB Write Inhibit B. When WIB is set to 1, writing into IPFB is inhibited.

WIA Write Inhibit A. When WIA is set to 1, writing into IPFA is inhibited.

WIS Write Inhibit S. When WIS is set to 1, writing into TCS is inhibited.

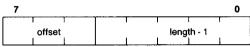

#### 2.2 MEMORY ORGANIZATION

The NS32GX320 implements full 32-bit addresses. This allows the device to access up to 4 Gbytes of memory. The memory is a uniform linear address space. Memory locations are numbered sequentially starting at zero and ending at 2<sup>32</sup> — 1. The number specifying a memory location is called an address. The contents of each memory location is a byte consisting of eight bits. Unless otherwise noted, diagrams in this document show data stored in memory with the lowest address on the right and the highest address on the left. Also, when data is shown vertically, the lowest address is at the top of a diagram and the highest address at the bottom of the diagram. When bits are numbered in a diagram, the least significant bit is given the number zero, and is shown at the right of the diagram. Bits are numbered in increasing significance and toward the left.

Byte at Address A

Two contiguous bytes are called a word. Except where noted, the least significant byte of a word is stored at the lower address, and the most significant byte of the word is stored at the next higher address. In memory, the address of a word is the address of its least significant byte, and a word may start at any address.

| 15  | 8 | 8 7 |  |  |  |

|-----|---|-----|--|--|--|

| A+1 |   | Α   |  |  |  |

| MSB |   | LSB |  |  |  |

#### Word at Address A

Two contiguous words are called a double-word. Except where noted, the least significant word of a double-word is stored at the lowest address and the most significant word of the double-word is stored at the address two higher. In memory, the address of a double-word is the address of its least significant byte, and a double-word may start at any address.

| 31  | 24 | 23  | 16 | 15  | 8 | 7   | 0 |

|-----|----|-----|----|-----|---|-----|---|

| A+3 |    | A+2 |    | A+1 |   | Α   |   |

| MSB |    |     |    |     |   | LSB |   |

#### Double-Word at Address A

Although memory is addressed as bytes, it is actually organized as double-words. Note that access time to a word or a double-word depends upon its address, e.g. double-words that are aligned to start at addresses that are multiples of four will be accessed more quickly than those not so aligned. This also applies to words that cross a double-word boundary.

#### 2.2.1 Address Mapping

Figure 2-15 shows the NS32GX320 address mapping.

The NS32GX320 supports the use of memory-mapped peripheral devices and coprocessors. Such memory-mapped devices can be located at arbitrary locations in the address space except for the upper 8 Mbytes of memory (addresses between FF800000 (hex) and FFFFFFF (hex), inclusive). which are reserved by National Semiconductor Corporation. Nevertheless, it is recommended that high-performance peripheral devices and coprocessors be located in a specific 8 Mbyte region of memory (addresses between FF000000 (hex) and FF7FFFFF (hex), inclusive), that is dedicated for memory-mapped I/O. This is because the NS32GX320 detects references to the dedicated locations and serializes reads and writes. See Section 3.1.3.3. When making I/O references to addresses outside the dedicated region, external hardware must indicate to the NS32GX320 that special handling is required. In this case a small performance degradation will also result. Refer to Section 3.1.3.2 for more information on memory-mapped I/O.

Address (Hex)

FIGURE 2-15. NS32GX320 Address Mapping

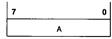

#### 2.3 MODULAR SOFTWARE SUPPORT

The NS32GX320 provides special support for software modules and modular programs.

Each module in a NS32GX320 software environment consists of three components:

- 1. Program Code Segment.

- This segment contains the module's code and constant data.

- 2. Static Data Segment.

Used to store variables and data that may be accessed by all procedures within the module.

3. Link Table.

This component contains two types of entries: Absolute Addresses and Procedure Descriptors.

An Absolute Address is used in the external addressing mode, in conjunction with a displacement and the current MOD Register contents to compute the effective address of an external variable belonging to another module.

The Procedure Descriptor is used in the call external procedure (CXP) instruction to compute the address of an external procedure.

Normally, the linker program specifies the locations of the three components. The Static Data and Link Table typically reside in RAM; the code component can be either in RAM or in ROM. The three components can be mapped into noncontiguous locations in memory, and each can be independently relocated. Since the Link Table contains the absolute addresses of external variables, the linker need not assign absolute memory addresses for these in the module itself; they may be assigned at load time.

To handle the transfer of control from one module to another, the NS32GX320 uses a module table in memory and two registers in the CPU.

The Module Table is located within the first 64 kbytes of memory. This table contains a Module Descriptor (also called a Module Table Entry) for each module in the address space of the program. A Module Descriptor has four 32-bit entries corresponding to each component of a module:

- The Static Base entry contains the address of the beginning of the module's static data segment.

- The Link Table Base points to the beginning of the module's Link Table.

- The Program Base is the address of the beginning of the code and constant data for the module.

- · A fourth entry is currently unused but reserved.

The MOD Register in the CPU contains the address of the Module Descriptor for the currently executing module.

The Static Base Register (SB) contains a copy of the Static Base entry in the Module Descriptor of the currently executing module, i.e., it points to the beginning of the current module's static data area.

This register is implemented in the CPU for efficiency purposes. By having a copy of the static base entry or chip, the CPU can avoid reading it from memory each time a data item in the static data segment is accessed.

In an NS32GX320 software environment modules need not be linked together prior to loading. As modules are loaded, a linking loader simply updates the Module Table and fills the Link Table entries with the appropriate values. No modification of a module's code is required. Thus, modules may be stored in read-only memory and may be added to a system independently of each other, without regard to their individual addressing. *Figure 2-16* shows a typical NS32GX320 run-time environment.

TL/EE/10564-2

Note: Dashed lines indicate information copied to registers during transfer of control between modules.

FIGURE 2-16. NS32GX320 Run-Time Environment

TL/EE/10564-3

FIGURE 2-17. General Instruction Format

FIGURE 2-18. Index Byte Format

TL/EE/10564-4

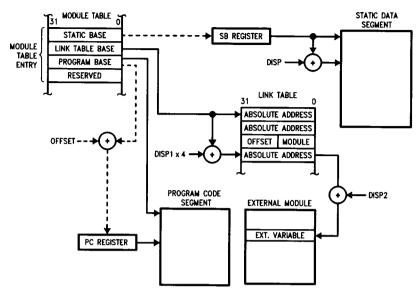

#### 2.4 INSTRUCTION SET

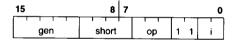

#### 2.4.1 General Instruction Format

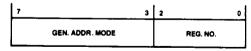

Figure 2-17 shows the general format of a Series 32000 instruction. The Basic Instruction is one to three bytes long and contains the Opcode and up to two 5-bit General Addressing Mode ("Gen") fields. Following the Basic Instruction field is a set of optional extensions, which may appear depending on the instruction and the addressing modes selected.

Index Bytes appear when either or both Gen fields specify Scaled Index. In this case, the Gen field specifies only the Scale Factor (1, 2, 4 or 8), and the Index Byte specifies which General Purpose Register to use as the index, and which addressing mode calculation to perform before indexing. See Figure 2-18.

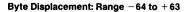

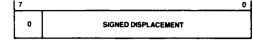

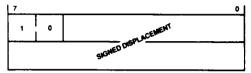

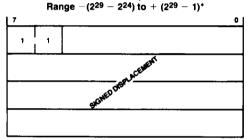

Following Index Bytes come any displacements (addressing constants) or immediate values associated with the selected addressing modes. Each Disp/Imm field may contain one or two displacements, or one immediate value. The size of a Displacement field is encoded with the top bits of that field, as shown in *Figure 2-19*, with the remaining bits interpreted as a signed (two's complement) value. The size of an immediate value is determined from the Opcode field. Both Displacement and Immediate fields are stored most significant byte first. Note that this is different from the memory representation of data (Section 2.2).

Some instructions require additional, 'implied' immediates and/or displacements, apart from those associated with addressing modes. Any such extensions appear at the end of the instruction, in the order that they appear within the list of operands in the instruction definition (Section 2.4.3).

#### 2.4.2 Addressing Modes

The CPU generally accesses an operand by calculating its Effective Address based on information available when the operand is to be accessed. The method to be used in performing this calculation is specified by the programmer as an "addressing mode."

#### Word Displacement: Range -8192 to +8191

## Double Word Displacement:

TL/EE/10564-5

#### FIGURE 2-19. Displacement Encodings

\*Note: The pattern "1110000" for the most significant byte of the displacement is reserved by National for future enhancements. Therefore, it should never be used by the user program. This causes the lower limit of the displacement range to be -(229 - 224) instead of -229.

Addressing modes are designed to optimally support highlevel language accesses to variables. In nearly all cases, a variable access requires only one addressing mode, within the instruction that acts upon that variable. Extraneous data movement is therefore minimized.

Addressing Modes fall into nine basic types:

Register: The operand is available in one of the eight General Purpose Registers. In certain Slave Processor instructions, an auxiliary set of eight registers may be referenced instead.

Register Relative: A General Purpose Register contains an address to which is added a displacement value from the instruction, yielding the Effective Address of the operand in memory.

**Memory Space:** Identical to Register Relative above, except that the register used is one of the dedicated registers PC, SP, SB or FP. These registers point to data areas generally needed by high-level languages.

**Memory Relative:** A pointer variable is found within the memory space pointed to by the SP, SB or FP register. A displacement is added to that pointer to generate the Effective Address of the operand.

**Immediate:** The operand is encoded within the instruction. This addressing mode is not allowed if the operand is to be written.

**Absolute:** The address of the operand is specified by a displacement field in the instruction.

**External:** A pointer value is read from a specified entry of the current Link Table. To this pointer value is added a displacement, yielding the Effective Address of the operand.

**Top of Stack:** The currently-selected Stack Pointer (SP0 or SP1) specifies the location of the operand. The operand is pushed or popped, depending on whether it is written or read.

**Scaled Index:** Although encoded as an addressing mode, Scaled Indexing is an option on any addressing mode except Immediate or another Scaled Index. It has the effect of

calculating an Effective Address, then multiplying any General Purpose Register by 1, 2, 4 or 8 and adding it into the total, yielding the final Effective Address of the operand.

Table 2-1 is a brief summary of the addressing modes. For a complete description of their actions, see the Instruction Set Reference Manual.

#### 2.4.3 Instruction Set Summary

Table 2-2 presents a brief description of the NS32GX320 instruction set. The Format column refers to the Instruction Format tables (Appendix A). The Instruction column gives the instruction as coded in assembly language, and the Description column provides a short description of the function provided by that instruction. Further details of the exact operations performed by each instruction may be found in the Instruction Set Reference Manual.

#### Notations:

i = Integer length suffix: B = Byte

W = Word

D = Double Word

f = Floating Point length suffix: F = Standard Floating

L = Long Floating

gen = General operand. Any addressing mode can be specified.

short = A 4-bit value encoded within the Basic Instruction (see Appendix A for encodings).

imm = Implied immediate operand. An 8-bit value appended after any addressing extensions.

disp = Displacement (addressing constant): 8, 16 or 32 bits. All three lengths legal.

reg = Any General Purpose Register: R0-R7.

areg = Any Processor Register: Address, Debug, Status, Configuration.

creg = A Custom Slave Processor Register (Implementation Dependent).

cond = Any condition code, encoded as a 4-bit field within the Basic Instruction (see Appendix A for encodings).

TABLE 2-1. NS32GX320 Addressing Modes

| ENCODING          | MODE                      | ASSEMBLER SYNTAX   | EFFECTIVE ADDRESS                        |

|-------------------|---------------------------|--------------------|------------------------------------------|

| Register          |                           |                    |                                          |

| 00000             | Register 0                | R0, F0, L0         | None: Operand is in the                  |

| 00001             | Register 1                | R1, F1, L1         | specified register.                      |

| 00010             | Register 2                | R2, F2, L2         |                                          |

| 00011             | Register 3                | R3, F3, L3         |                                          |

| 00100             | Register 4                | R4, F4, L4         |                                          |

| 00101             | Register 5                | R5, F5, L5         |                                          |

| 00110             | Register 6                | R6, F6, L6         |                                          |

| 00111             | Register 7                | R7, F7, L7         |                                          |

| Register Relative |                           |                    |                                          |

| 01000             | Register 0 relative       | disp(R0)           | Disp + Register.                         |

| 01001             | Register 1 relative       | disp(R1)           |                                          |

| 01010             | Register 2 relative       | disp(R2)           |                                          |

| 01011             | Register 3 relative       | disp(R3)           |                                          |

| 01100             | Register 4 relative       | disp(R4)           |                                          |

| 01101             | Register 5 relative       | disp(R5)           |                                          |

| 01110             | Register 6 relative       | disp(R6)           |                                          |

| 01111             | Register 7 relative       | disp(R7)           |                                          |

| Memory Relative   | <b>3</b>                  |                    |                                          |

| 10000             | Frame memory relative     | disp2(disp1(FP))   | Disp2 + Pointer; Pointer found at        |

| 10001             | Stack memory relative     | disp2(disp1(SP))   | address Disp1 + Register. "SP" is either |

| 10010             | Static memory relative    | disp2(disp1(SB))   | SP0 or SP1, as selected in PSR.          |

| Reserved          | Ciallo momory relative    | dispe(disp ((OD))  | or o or or 1, as selected in 1 or 1.     |

| 10011             | (Reserved for Future Use) |                    |                                          |

|                   | (Neserved for Future Ose) |                    |                                          |

| Immediate         | J#:                       |                    | Name Oracle Block and                    |

| 10100             | Immediate                 | value              | None. Operand is input from              |

|                   |                           |                    | instruction queue.                       |

| Absolute          |                           |                    |                                          |

| 10101             | Absolute                  | @disp              | Disp.                                    |

| External          |                           |                    |                                          |

| 10110             | External                  | EXT(disp1) + disp2 | Disp2 + Pointer; Pointer is found        |

|                   |                           |                    | at Link Table Entry number Disp1.        |

| Top of Stack      |                           |                    |                                          |

| 10111             | Top of stack              | TOS                | Top of current stack, using either       |

|                   |                           |                    | User or Interrupt Stack Pointer,         |

|                   |                           |                    | as selected in PSR. Automatic            |

|                   |                           |                    | Push/Pop included.                       |

| Memory Space      |                           |                    |                                          |

| 11000             | Frame memory              | disp(FP)           | Disp + Register; "SP" is either          |

| 11001             | Stack memory              | disp(SP)           | SP0 or SP1, as selected in PSR.          |

| 11010             | Static memory             | disp(SB)           | • •                                      |

| 11011             | Program memory            | * + disp           |                                          |

| Scaled Index      | <b>5</b>                  | •                  |                                          |

| 11100             | Index, bytes              | mode[Rn:B]         | EA (mode) + Rn.                          |

| 11101             | Index, words              | mode[Rn:W]         | EA (mode) + $2 \times Rn$ .              |

| 11110             | Index, double words       | mode[Rn:D]         | EA (mode) $+ 4 \times \text{Rn}$ .       |

| 11111             | Index, quad words         | mode[Rn:Q]         | EA (mode) $+ 8 \times \text{Rn}$ .       |

|                   | maon, quad morus          | ocoli m.os         | 'Mode' and 'n' are contained             |

|                   |                           |                    | within the Index Byte.                   |

|                   |                           |                    | EA (mode) denotes the effective          |

|                   |                           |                    | , ,                                      |

|                   |                           |                    | address generated using mode.            |

## TABLE 2-2. NS32GX320 Instruction Set Summary

|         |                           | TABLE              | 2-2. NS32GX320 Instruction Set Summary                            |

|---------|---------------------------|--------------------|-------------------------------------------------------------------|

| MOVES   |                           |                    |                                                                   |

| Format  | Operation                 | Operands           | Description                                                       |

| 4       | MOVi                      | gen,gen            | Move a value.                                                     |

| 2       | MOVQi                     | short,gen          | Extend and move a signed 4-bit constant.                          |

| 7       | MOVMi                     | gen,gen,disp       | Move Multiple: disp bytes (1 to 16).                              |

| 7       | MOVZBW                    | gen,gen            | Move with zero extension.                                         |

| 7       | MOVZID                    | gen,gen            | Move with zero extension.                                         |

| 7       | MOVXBW                    | gen,gen            | Move with sign extension.                                         |

| 7       | MOVXID                    | gen,gen            | Move with sign extension.                                         |

| 4       | ADDR                      | gen,gen            | Move Effective Address.                                           |

|         | ARITHMETIC                |                    |                                                                   |

| Format  | Operation                 | Operands           | Description                                                       |

| 4       | ADDI                      | gen,gen            | Add.                                                              |

| 2       | ADDQi                     | short,gen          | Add signed 4-bit constant.                                        |

| 4       | ADDCi                     | gen,gen            | Add with carry.                                                   |

| 4       | SUBi                      | gen,gen            | Subtract.                                                         |

| 4       | SUBCi                     | gen,gen            | Subtract with carry (borrow).                                     |

| 6<br>6  | NEGi                      | gen,gen            | Negate (2's complement).                                          |

| 7       | ABSi                      | gen,gen            | Take absolute value.                                              |

| 7       | MULi<br>QUOi              | gen,gen            | Multiply.                                                         |

| 7       | REMi                      | gen,gen            | Divide, rounding toward zero.                                     |

| 7       | DIVi                      | gen,gen            | Remainder from QUO.                                               |

| 7       | MODi                      | gen,gen            | Divide, rounding down.                                            |

| 7       | MEII                      | gen,gen            | Remainder from DIV (Modulus). Multiply to Extended Integer.       |

| 7       | DEIi                      | gen,gen<br>gen,gen | Divide Extended Integer.                                          |

| ,<br>18 | MULWD                     | gen,gen            | Multiply Word to Double.                                          |

| 18      | MACTD                     | gen,gen            | Multiply and Accumulate Twice Double.                             |

|         | K ARITHMETIC              |                    | wattiply and Accumulate Twice Double.                             |

| Format  | Operation                 | Operands           | Description                                                       |

| 18      | CMULD                     | gen,gen            | Complex Multiply Double.                                          |

| 18      | CMACD                     | gen,gen            | Complex Multiply Double.  Complex Multiply and Accumulate Double. |

|         |                           |                    | Complex Multiply and Accumulate Double.                           |

| Format  | -                         | ) ARITHMETIC       | December                                                          |

| 6       | <b>Operation</b><br>ADDPi | Operands           | Description Add Packed.                                           |

| 6       | SUBPi                     | gen,gen            | Subtract Packed.                                                  |

|         |                           | gen,gen            | Subtract Packed.                                                  |

|         | COMPARISON                |                    | <b>.</b>                                                          |

| Format  | Operation                 | Operands           | Description                                                       |

| 4       | CMPi                      | gen,gen            | Compare.                                                          |

| 2<br>7  | CMPQi                     | short,gen          | Compare to signed 4-bit constant.                                 |

|         | CMPMi                     | gen,gen,disp       | Compare Multiple: disp bytes (1 to 16).                           |

|         | AND BOOLEA                |                    |                                                                   |

| Format  | Operation                 | Operands           | Description                                                       |

| 4       | ANDi                      | gen,gen            | Logical AND.                                                      |

| 4       | ORi                       | gen,gen            | Logical OR.                                                       |

| 4       | BICi                      | gen,gen            | Clear selected bits.                                              |

| 4       | XORi                      | gen,gen            | Logical Exclusive OR.                                             |

| 6       | COMI                      | gen,gen            | Complement all bits.                                              |

| 6<br>2  | NOTi<br>Scondi            | gen,gen            | Boolean complement: LSB only.                                     |

| _       | Scondi                    | gen                | Save condition code (cond) as a Boolean variable of size i.       |

| SHIFTS  | <b>.</b>                  |                    | <b>.</b>                                                          |

| Format  | Operation                 | Operands           | Description                                                       |

| 6       | LSHi                      | gen,gen            | Logical Shift, left or right.                                     |

| 6       | ASHi                      | gen,gen            | Arithmetic Shift, left or right.                                  |

| 6       | ROTi                      | gen,gen            | Rotate, left or right.                                            |

|         |                           |                    |                                                                   |

## TABLE 2-2. NS32GX320 Instruction Set Summary (Continued)

| BITS   |           |          |                                  |

|--------|-----------|----------|----------------------------------|

| Format | Operation | Operands | Description                      |

| 4      | TBITi     | gen,gen  | Test bit.                        |

| 6      | SBITi     | gen,gen  | Test and set bit.                |

| 6      | SBITIi    | gen,gen  | Test and set bit, interlocked.   |

| 6      | CBITi     | gen,gen  | Test and clear bit.              |

| 6      | CBITIi    | gen,gen  | Test and clear bit, interlocked. |

| 6      | IBITi     | gen,gen  | Test and invert bit.             |

| 8      | FFSi      | gen,gen  | Find first set bit.              |

#### **BIT FIELDS**

SKPSi

SKPST

options

options

5

Rit fields are values in memory that are not aligned to byte boundaries. Examples are PACKED arrays and records used in

| Format      | Operation        | Operands              | Description                                              |                                           |  |  |  |

|-------------|------------------|-----------------------|----------------------------------------------------------|-------------------------------------------|--|--|--|

| 8           | EXTi             | reg,gen,gen,disp      | Extract bit field (array oriented).                      |                                           |  |  |  |

| 8           | INSi             | reg,gen,gen,disp      | Insert bit field (array oriented).                       |                                           |  |  |  |

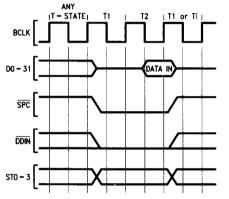

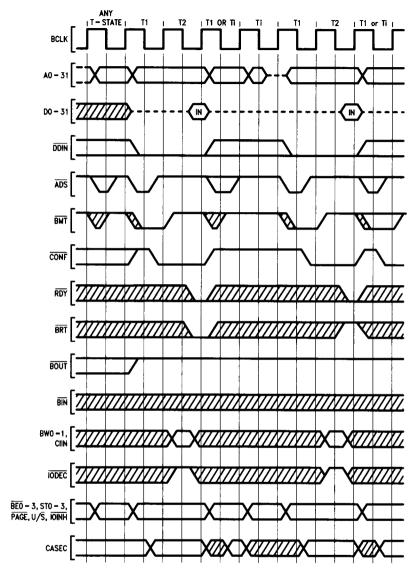

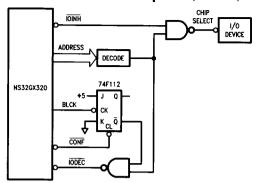

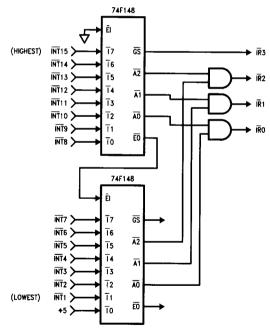

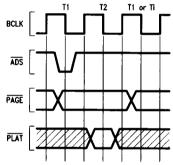

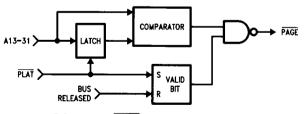

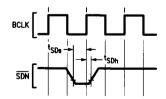

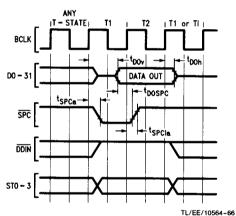

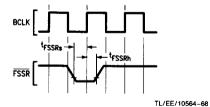

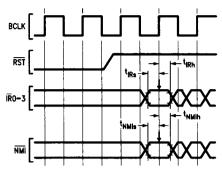

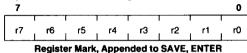

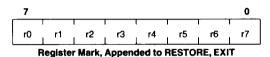

| 7           | EXTSi            | gen,gen,imm,imm       | Extract bit field (short form).                          |                                           |  |  |  |