PRELIMINARY

April 1988

# NS32580-20/NS32580-25/NS32580-30 Floating Point Controller

# **General Description**

The NS32580 Floating-Point Controller (FPC) is an interface controller designed to couple the NS32532 Microprocessor with the Weitek WTL 3164 Floating-Point Data Path (FPDP). It is a new member of the Series 32000® family and it is fully upward compatible with the existing NS32081 floating-point software. The performance of the NS32580 (FPC) and the WTL 3164 (FPDP) with the NS32532 has been significantly enhanced for high-performance floating-point applications. It reaches the peak performance of 15 Mflops when executing single and double precision ADD, SUB, MUL, and MAC instructions in a pipelined mode while maintaining precise exception handling.

The FPC/FPDP supports the IEEE 754—1985 standard for Binary Floating-Point Arithmetic. An improved exception handling scheme allows enabling or disabling of each of the IEEE defined traps. It supports Infinity and Not a Number (NaN) and can flush the result to zero or trap on underflowed instructions.

The NS32580 contains three FIFOs and a Floating-Point Status Register (FSR). It executes 18 instructions in conjunction with the WTL 3164 and with the NS32532 forms a tightly coupled computer cluster. The FPC/FPDP appears to the user as a single slave processing unit. All addressing modes, including two address operations, are available with the floating-point instructions. In addition, the CPU and

FPC/FPDP communication is handled automatically, and is user transparent.

The FPC is fabricated with National's advanced double-metal CMOS process and can operate at a frequency of 30 MHz.

#### **Features**

- Provides the NS32532 CPU with a complete interface controller for high-speed floating-point arithmetic

- 15 Mflops peak performance for single and double precision ADD, SUB, MUL and MAC instructions with the Weitek WTL 3164 FPDP

- Conforms to IEEE 754—1985 standard for Binary Floating-Point Arithmetic

- Pipelined Slave Protocol with Data and Instruction FIFOs

- Improved exception handling including support of Infinities and Not a Number (NaN)

- Single (32-bit) and double (64-bit) precision operations

- Upward compatible with existing NS32081 software base

- 20 MHz, 25 MHz and 30 MHz operating frequencies

- 1 µm double-metal CMOS technology

- 172-pin PGA package

© 1988 National Semiconductor Corporation TL/EE/942

RRD-B20M48/Printed in U. S. A

### **Table of Contents**

#### 1.0 PRODUCT INFORMATION

- 1.1 IEEE Features Supported

- 1.2 Operand Formats

- 1.2.1 Normalized Numbers

- 1227ero

- 1.2.3 Reserved Operands

- 1.2.4 Integer Formats

- 1.2.5 Memory Representations

#### 2.0 ARCHITECTURAL DESCRIPTION

- 2.1 Programming Model

- 2.1.1 Floating-Point Data Registers

- 2.1.2 Floating-Point Status Register (FSR)

- 2.1.2.1 FSR Mode Control Fields

- 2.1.2.2 FSR Status Fields

- 2.1.2.3 FSR Software Field (SWF)

- 2.1.2.4 FSR New Fields

- 2.1.2.5 FSR Default Values

- 2.2 Instruction Set

- 2.2.1 General Instruction Format

- 2.2.2 Addressing Modes

- 2.2.3 Floating-Point Instruction Set

- 2.3 Exceptions/TRAPs

#### 3.0 FUNCTIONAL DESCRIPTION

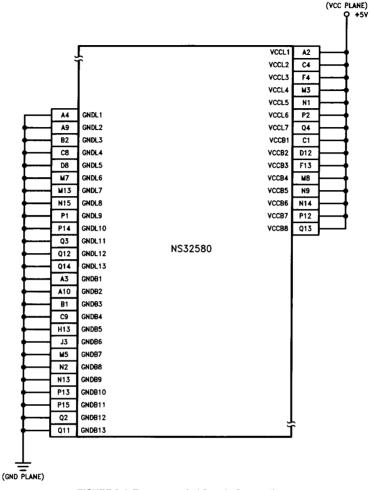

- 3.1 Power and Grounding

- 3.2 Clocking

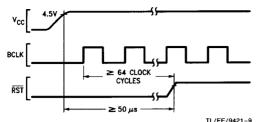

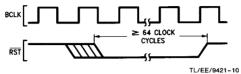

- 3.3 Resetting

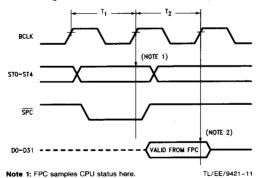

- 3.4 Bus Operation

- 3.4.1 Operand Transfers

#### 3.0 FUNCTIONAL DESCRIPTION (Continued)

- 3.5 Instruction Protocols

- 3.5.1 General Slave Protocol Sequence

- 3.5.2 Pipelined Slave Protocol Sequence

- 3.5.3 Status Word Register

- 3.5.4 Termination of Instruction (Not Including CMPF)

- 3.5.5 Byte Sex

- 3.5.6 Floating-Point Protocols

- 3.6 FPDP Interface

- 3.6.1 Controlling the FPDP

- 3.6.2 Instruction Control

- 3.6.3 "2 Cycle Mode" and "3 Cycle Mode"

- 3.6.4 FPDP Mode Control Registers SR0, SR1

- 3.6.5 IEEE Enables Register SR2

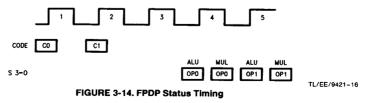

- 3.6.5.1 FPDP Status Lines (S0-S3)

- 3.6.6 FPC-FPDP Clocks

- 3.6.6.1 FPC Clock

- 3.6.6.2 FPDP Main Clock (WCLK)

- 3.6.6.3 Divide/Sqrt Unit Clock (DIVCLK)

#### 4.0 DEVICE SPECIFICATIONS

- 4.1 NS32580 Pin Descriptions

- 4.1.1 Supplies

- 4.1.2 Input Signals

- 4.1.3 Output Signals

- 4.1.4 Input/Output Signals

- 4.2 Absolute Maximum Ratings

- 4.3 Electrical Characteristics

- 4.4 Switching Characteristics

- 4.4.1 Definitions

- 4.4.2 Timing Tables

- 4.4.2.1 Output Signal Propagation Delays

- 4.4.2.2 Input Signal Requirements

APPENDIX A: Compatibility of FPC-FPDP with NS32081/ NS32381 Performance Analysis

# **List of Illustrations**

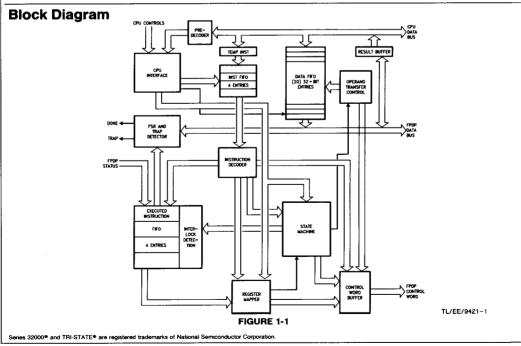

| FPC Block Diagram                                                |

|------------------------------------------------------------------|

| Floating-Point Operand Formats                                   |

| Single-Precision Operand E and F Fields with Quiet NaN Format    |

| Double-Precision Operand E and F Fields with Quiet NaN Format1-4 |

| Integer Format                                                   |

| Data Registers                                                   |

| FSR (Compatible Fields)                                          |

| New FSR Mode Control Fields                                      |

| General Instruction Format2-4                                    |

| Index Byte Format                                                |

| Displacement Encodings                                           |

| Floating-Point Instruction Formats                               |

| Recommended Supply Connections                                   |

| Power-On Reset Requirements                                      |

| General Reset Timing                                             |

| Slave Processor Read Cycle from FPC                              |

| Slave Processor Write Cycle to FPC                               |

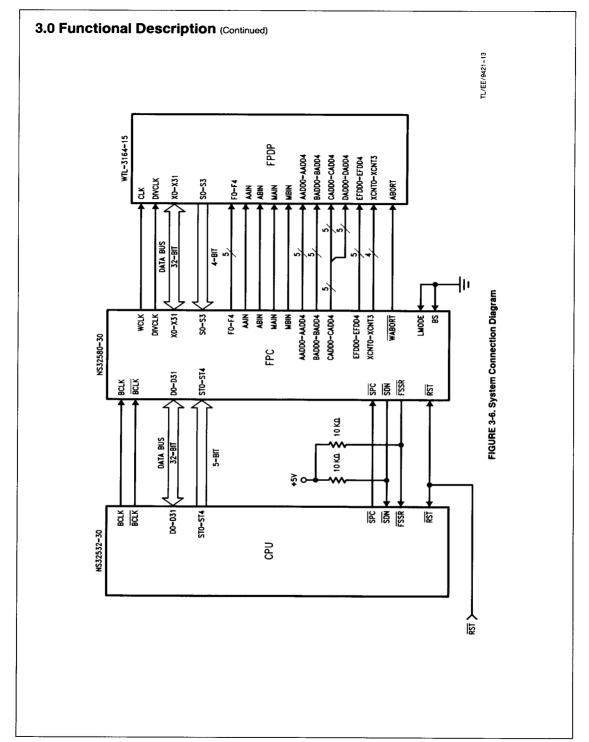

| System Connection Diagram                                        |

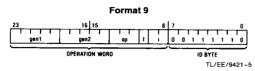

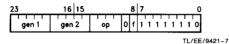

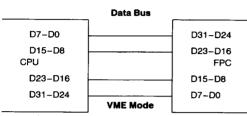

| ID and Opcode Format                                             |

| 32-Bit General Slave Instruction Protocol                        |

| FPC Status Word Format                                           |

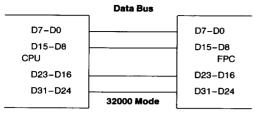

| Byte Sex Connection Diagrams                                     |

| FPDP Control Word                                                |

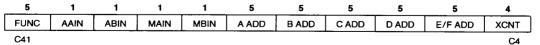

| FPDP Multiplier and ALU Bus Control                              |

| IEEE Enables Register (FPDP)                                     |

| FPDP Status Timing                                               |

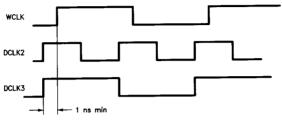

| Divide/Sqrt Clock DCLK2/DCLK3                                    |

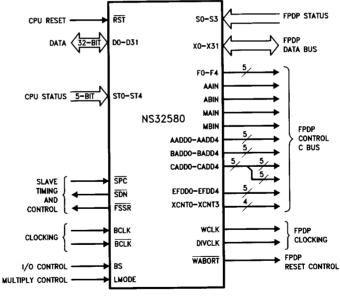

| NS32580 Interface Signals4-1                                     |

| 172-Pin PGA Package                                              |

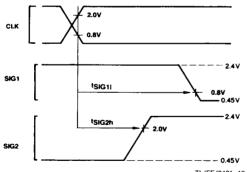

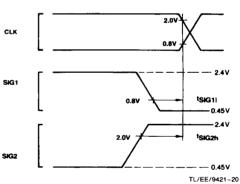

| Timing Specification Standard (Signal Valid after Clock Edge)    |

| Timing Specification Standard (Signal Valid before Clock Edge)   |

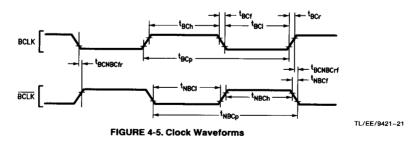

| Clock Waveforms4-5                                               |

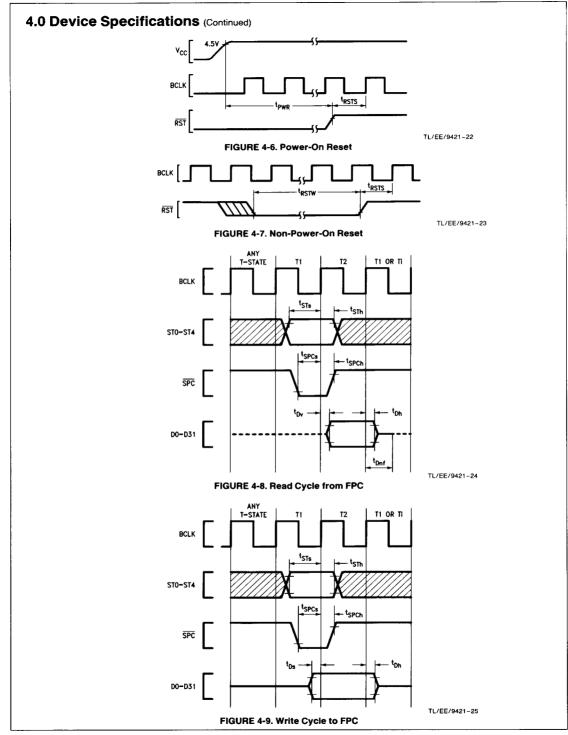

| Power-On Reset                                                   |

| Non-Power-On Reset                                               |

| Read Cycle from FPC                                              |

| Write Cycle to FPC4-9                                            |

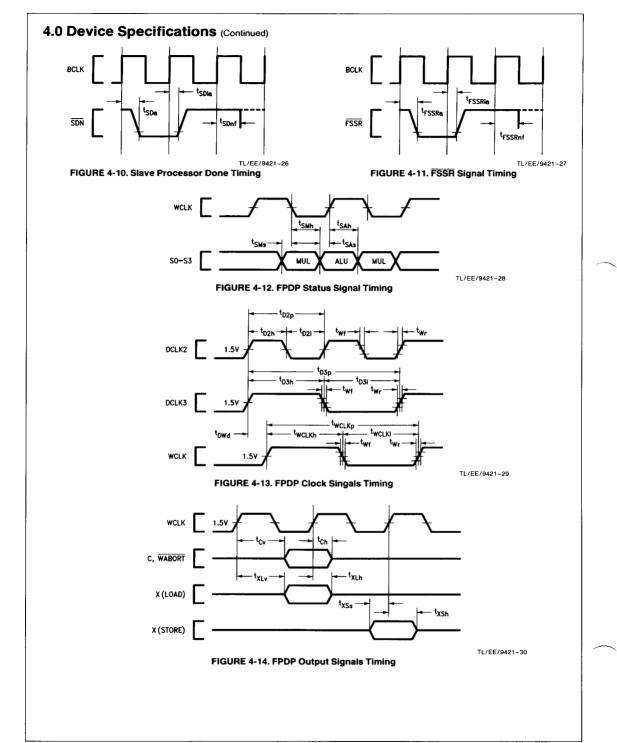

| Slave Processor Done Timing4-10                                  |

| FSSR Signal Timing4-11                                           |

| FPDP Status Signal Timing4-12                                    |

| FPDP Clock Signals Timing4-13                                    |

| FPDP Output Signals Timing4-14                                   |

| List of Tables                                                   |

| Sample F Fields                                                  |

| Sample E Fields                                                  |

| Normalized Number Ranges                                         |

| Integer Fields                                                   |

| FSR Default State Summary                                        |

| Series 32000 Family Addressing Modes                             |

| Exception Enabled/Disabled Summary2-3                            |

| 32-Bit General Slave Instruction Protocol                        |

| Floating-Point Instruction Protocols                             |

|                                                                  |

### 1.0 Product Information

The NS32580 Floating-Point Controller (FPC) provides complete control for high speed floating-point operations between the NS32532 CPU and the Weitek WTL 3164 Floating-Point Data Path (FPDP). The FPC is fabricated using National high-speed CMOS technology and operates as a slave processor for transparent expansion of the Series 32000 CPU's basic instruction set. The NS32580 is compatible with the IEEE Floating-Point Formats by means of its hardware and software features.

#### 1.1 IEEE FEATURES SUPPORTED

- a. Basic floating-point number formats

- Add, subtract, multiply, divide, sqrt, and compare operations

- c. Conversions between different floating-point formats

- d. Conversions between floating-point and integer formats

- e. Round floating-point number to integer (round to nearest, round toward infinities and round toward zero, in double- or single-precision)

- f. Exception signaling and handling (invalid operation, divide by zero, overflow, underflow and inexact)

- g. Positive and negative infinity and Not-a-Number (NaN) (Section 1.2.3)

Note: In addition to supporting the IEEE floating-point overflow, the NS32580 supports integer conversion overflow.

The remaining IEEE features are supported in the software library. These items include:

- a. Extended floating-point number formats

- b. Mixed floating-point data formats

- Conversions between basic formats, floating-point numbers and decimal strings

- d. Remainder

- e. Denormalized numbers

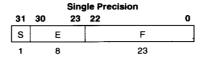

#### 1.2 OPERAND FORMATS

The NS32580 FPC operates on two floating-point data types—single precision (32 bits) and double precision (64 bits). Floating-point instruction mnemonics use the suffix F (Floating) to select the single precision data type, and the suffix L (Long Floating) to select the double precision data type.

A floating-point number is divided into three fields, as shown in *Figure 1-2*.

The F field is the fractional portion of the represented number. In Normalized numbers (Section 1.2.1), the binary point is assumed to be immediately to the left of the most significant bit of the F field, with an implied 1 bit to the left of the binary point. Thus, the F field represents values in the range  $1.0 \le x \le 2.0$ , as shown in Table 1-1.

TABLE 1-1. Sample F Fields

|         | oup.o        |               |

|---------|--------------|---------------|

| F Field | Binary Value | Decimal Value |

| 000 0   | 1.000 0      | 1.000 0       |

| 0100    | 1.010 0      | 1.250 0       |

| 100 0   | 1.100 0      | 1.500 0       |

| 1100    | 1.110 0      | 1.750 0       |

|         | <b>↑</b>     |               |

| Impli   | ed Bit       |               |

The E field contains an unsigned number that gives the binary exponent of the represented number. The value in the E field is biased; that is, a constant bias value must be subtracted from the E field value in order to obtain the true exponent. The bias value is 011 . . . 11<sub>2</sub>, which is either 127 (single precision) or 1023 (double precision). Thus, the true exponent can be either positive or negative, as shown in Table 1-2.

TABLE 1-2. Sample E Fields

| E Field | F Field | Represented Value          |

|---------|---------|----------------------------|

| 011 110 | 100 0   | $1.5 \times 2^{-1} = 0.75$ |

| 011 111 | 100 0   | $1.5 \times 2^0 = 1.50$    |

| 100 000 | 100 0   | $1.5 \times 2^{1} = 3.00$  |

Two values of the E field are not exponents. 11 . . . 11 signals Not-a-Number (NaN) or Infinity (Section 1.2.3). 00 . . . . 00 represents the number zero (Section 1.2.2), if the F field is also all zeroes, otherwise it signals a reserved operand (Section 1.2.4).

The S bit indicates the sign of the operand. It is 0 for positive and 1 for negative. Floating-point numbers are in sign-magnitude form, that is, only the S bit is complemented in order to change the sign of the represented number.

#### 1.2.1 Normalized Numbers

Normalized numbers are numbers which can be expressed as floating-point operands, as described above, where the E field is neither all zeroes nor all ones.

The value of a Normalized number can be derived by the formula:

$$(-1)^S \times 2(E-Bias) \times (1 + F)$$

The range of Normalized numbers is given in Table 1-3.

#### 1.2.2 Zero

There are two representatives for zero—positive and negative. Positive zero has all-zero F and E fields, and the S bit is zero. Negative zero also has all-zero F and E fields, but its S bit is one

#### 1.2.3 Reserved Operands

NaN is a symbolic entity which is defined to have two types, Signaling NaN and Quiet NaN. The NS32580 can accept any form of NaN as operands but will only return Quiet NaN as a result.

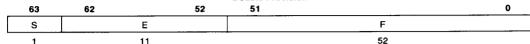

Infinity arithmetic is the limiting case of real arithmetic with operands of arbitrarily large magnitudes. The NS32580 does not treat infinity as a reserved operand and is fully supported per the IEEE standard. See Figures 1-3 and 1-4.

The NS32580 FPC treats only Denormalized numbers as reserved operands if the Floating-Point Status Register ROE bit is set (Section 2.1.2). Denormalized numbers have all zeroes in their E fields and non-zero values in their F fields.

The NS32580 FPC causes an Invalid Operation Trap (Section 2.1.2.2) if it receives a reserved operand, unless the operation is simply a move (without conversion).

#### Double Precision

FIGURE 1-2. Floating-Point Operand Formats

#### **TABLE 1-3. Normalized Number Ranges**

|                | Single Precision                | Double Precision                         |

|----------------|---------------------------------|------------------------------------------|

| Most Positive  | $2^{127} \times (2 - 2^{-23})$  | $2^{1023} \times (2 - 2^{-52})$          |

|                | $= 3.40282346 \times 10^{38}$   | $= 1.7976931348623157 \times 10^{308}$   |

| Least Positive | 2-126                           | 2-1022                                   |

|                | $= 1.17549436 \times 10^{-38}$  | $= 2.2250738585072014 \times 10^{-308}$  |

| Least Negative | - (2 <sup>-126</sup> )          | - (2 <sup>-1022</sup> )                  |

| ŭ              | $= -1.17549436 \times 10^{-38}$ | $= -2.2250738585072014 \times 10^{-308}$ |

| Most Negative  | $-2^{127} 	imes (2-2^{-23})$    | $-2^{1023} \times (2-2^{-52})$           |

| J              | $= -3.40282346 \times 10^{38}$  | $= -1.7976931348623157 \times 10^{308}$  |

Note: The values given are extended one full digit beyond their represented accuracy to help in generating rounding and conversion algorithms.

| E     | F     | Value                             | Name                | Comments                               |

|-------|-------|-----------------------------------|---------------------|----------------------------------------|

| 255   | Not 0 | None                              | NaN                 | ROE = 0 → Reserved Operand             |

|       |       |                                   |                     | ROE = 1 → Quiet NaN Returned as Result |

| 255   | 0     | (-1)s * Infinity                  | Infinity            | Not a Reserved Operand                 |

| 1-254 | Апу   | (-1)s * 20-127 * (1.f)            | Normalized Number   |                                        |

| 0     | Not 0 | (-1)s * 2 <sup>-126</sup> * (0.f) | Denormalized Number | Reserved Operand                       |

| 0     | 0     | (-1)s * 0                         | Zero                |                                        |

FIGURE 1-3. Single-Precision Operand E and F Fields with Quiet NaN Format

| E      | F     | Value                   | Name                | Comments                               |

|--------|-------|-------------------------|---------------------|----------------------------------------|

| 2047   | Not 0 | None                    | NaN                 | ROE = 0 → Reserved Operand             |

|        | İ     |                         |                     | ROE = 1 → Quiet NaN Returned as Result |

| 2047   | 0     | (-1)s * Infinity        | Infinity            | Not a Reserved Operand                 |

| 1-2046 | Any   | (-1)s * 20-1023 * (1.f) | Normalized Number   |                                        |

| 0      | Not 0 | (-1)s * 2-1022 * (0.f)  | Denormalized Number | Reserved Operand                       |

| 0      | 0     | (-1)s * 0               | Zero                |                                        |

FIGURE 1-4. Double-Precision Operand E and F Fields with Quiet NaN Format

# 1.0 Product Information (Continued)

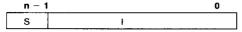

#### 1.2.4 Integer Formats

The FPC-FPDP performs conversions between integer and floating point operands. Integers are accepted and generated by the FPC-FPDP as two's complement values of byte (8 bits), word (16 bits) or double-word (32 bits).

FIGURE 1-5. Integer Format

TABLE 1-4. Integer Fields

| s | Value              | Name             |

|---|--------------------|------------------|

| 0 | ı                  | Positive Integer |

| 1 | I — 2 <sup>n</sup> | Negative Integer |

n represents number of bits in the word, 8 for byte, 16 for word and 32 for double-word.

The FPDP supports only 32-bit integers, therefore, the FPC has to sign extend 8- and 16-bit integers prior to integer to floating-point number conversion.

In floating to integer conversion, FPC has to check possible integer overflow, in case of 8- and 16-bit integer formats.

#### 1.2.5 Memory Representations

The NS32580 FPC does not directly access memory. However, it is cooperatively involved in the execution of a set of two-address instructions with the NS32532 CPU. The CPU determines the representation of operands in memory.

In the Series 32000 family of CPUs, operands are stored in memory with the least significant byte at the lowest byte address. The only exception to this rule is the Immediate addressing mode, where the operand is held (within the instruction format) with the most significant byte at the lowest address.

# 2.0 Architectural Description

#### 2.1 PROGRAMMING MODEL

The Series 32000 architecture includes nine registers; eight data registers and one floating-point status register.

#### 2.1.1 Floating-Point Data Registers (L0-L7)

There are eight registers (L0-L7) in the FPDP for providing high-speed access to floating-point operands. Each is 64 bits long. A floating-point register is referenced whenever a floating-point instruction uses the Register addressing mode (Section 2.2.2) for a floating-point operand. All other Register mode usages (i.e., integer operands) refer to the General Purpose Registers (R0-R7) of the CPU, and the FPU transfers the operand as if it were in memory.

Note: These registers are all upward compatible with the 32-bit NS32081 registers, (FO-F7), such that when the Register addressing mode is specified for a double precision (64-bit) operand, a pair of 32-bit registers holds the operand. The programmer specifies the even register of the pair which contains the least significant half of the operand and the next consecutive register contains the most significant half.

#### 2.1.2 Floating-Point Status Register (FSR)

The Floating-Point Status Register selects operating modes and records any exceptional condition encountered during execution of a floating-point operation. The FPC FSR contains all the NS32081/NS32381 FSR bits and additional fields for better exception handling. The FSR is cleared to all zeros during reset.

| DATA |            |         |    |  |  |

|------|------------|---------|----|--|--|

|      | <b>←</b> € | 54 →    |    |  |  |

|      | ← 32 →     | ← 32 →  |    |  |  |

| F1   | L0 MSDW    | L0 LSDW | F0 |  |  |

|      | L1 MSDW    | L1 LSDW |    |  |  |

| F3   | L2 MSDW    | L2 LSDW | F2 |  |  |

|      | L3 MSDW    | L3 LSDW |    |  |  |

| F5   | L4 MSDW    | L4 LSDW | F4 |  |  |

|      | L5 MSDW    | L5 LSDW |    |  |  |

| F7   | L6 MSDW    | L6 LSDW | F6 |  |  |

|      | L7 MSDW    | L7 LSDW |    |  |  |

LSDW → Least Significant Double Word

MSDW → Most Significant Double Word

FIGURE 2-1. Data Registers

#### 2.1.2.1 FSR Mode Control Fields

The FSR mode control fields select FPC operation modes. The meanings of the FSR mode control bits are given below:

ROUNDING MODE (RM bit 8-7). This field selects the rounding method. Floating-point results are rounded whenever they cannot be represented exactly. The rounding modes are:

- 00 Round to nearest value. The value which is nearest to the exact result is returned. If the result is exactly halfway between the two nearest values the even value (lsb = 0) is returned.

- 01 Round toward zero. The nearest value which is closer to zero or equal to the exact result is returned.

- 10 Round toward positive infinity. The nearest value which is greater than or equal to the result is returned.

- 11 Round toward negative infinity. The nearest value which is less than or equal to the exact result is returned

UNDERFLOW TRAP ENABLE (UEN bit 3). If this bit is set, the FPC requests a trap whenever a result is too small in absolute value to be presented as a Normalized number. If it is not set, FPC returns a result of exactly zero.

INEXACT RESULT TRAP ENABLE (IEN bit 5). If this bit is set, the FPC requests a trap whenever the result of an operation cannot be represented exactly in the operand format of the destination (and no other exception occurred in the same operation) or if the result of an operation overflows and the overflow trap is disabled. If IEN is not set, the result is rounded according to the selected rounding mode.

#### 2.1.2.2 FSR Status Fields

The FSR Status Fields record exceptional conditions encountered during floating-point data processing. The meaning of the FSR status bits are given below:

TRAP TYPE (TT bits 2–0). This 3-bit field indicates the reason for TRAP (FPU) requested by the FPC. The TT field is loaded with zero whenever any floating-point instruction except LFSR or SFSR completes without exception. It is also set to zero by a reset or by writing zero into it with the LFSR instruction. The TT field is updated regardless of the setting of the exception enable bits.

| 31         | 17 16 | 15  | 9 8 | 7 6  | 5   | 4 3   | 2   | 0  |  |

|------------|-------|-----|-----|------|-----|-------|-----|----|--|

| New Fields | RMB   | SWF | RN  | / IF | IEN | UF UE | N 1 | тт |  |

#### FIGURE 2-2. FSR (Compatible Fields)

- 000 No exceptional condition occurred.

- 001 Underflow. This condition occurs whenever a result is too close to zero to be represented as a Normalized number.

- 010 Overflow. This condition occurs whenever a result is too large in absolute value to be represented (float or integer).

- 011 Divide by Zero. This condition occurs whenever an attempt was made to divide a non-zero value by zero.

- 100 Illegal Instruction. An illegal or undefined Floating-Point instruction was passed to the FPC.

- 101 Invalid Operation. This condition occurs if:

- NaN is used as a floating-point operand by any instruction except MOVf and the Reserved Operand Enable (ROE) bit in the FSR is disabled.

- DNRM is used as a floating-point operand by any instruction except MOVf.

- 3. Both operands of the DIVf instruction are zero.

- 4. Sgrt when the floating-point number is negative.

- 5. Infinity plus negative infinity, infinity minus infinity.

- 110 Inexact Result. This condition occurs whenever the result of an operation cannot be exactly represented in the precision of the destination (and no other exception occurred in the same operation) or if the result of an operation overflows (floating-point or integer conversion overflow) and the overflow trap is disabled.

#### 111 Reserved.

UNDERFLOW FLAG (UF bit 4). This bit is set by the FPC whenever a result is too small in absolute value to be represented as a Normalized number. Its function is not affected by the state of the UEN bit. The UF bit is "sticky" therefore it can be cleared only by writing a zero into it with the Load FSR instruction or by a hardware reset.

INEXACT RESULT FLAG (IF bit 6). This bit is set by the FPC whenever the result of an operation must be rounded to fit within the destination format (and no other exception occurred in the same operation) or if the result of an operation overflows and the overflow trap is disabled. This situation applies both to floating-point and integer destinations. The IF bit is "sticky" therefore it is cleared only by writing a zero into it with the Load FSR instruction or by a hardware reset

REGISTER MODIFY BIT (RMB BIT 16). This bit is set by the FPC whenever writing to a floating-point data register. The RMB bit is cleared only by writing a zero with the LFSR instruction or by a hardware reset. This bit can be used in context switching to determine whether the FPC registers should be saved.

#### 2.1.2.3 FSR Software Field (SWF)

Bits 15-9 of the FSR hold and display any information written to them using the LFSRs and SFSR, but are not otherwise used by FPC hardware. They are reserved for use with NSC floating-point extension software.

#### 2.1.2.4 FSR New Fields

New fields were added to the FSR for better exception handling. In the FPC, the user can enable or disable each exception or combination of exceptions by using new "enable bits" implemented in the FSR. After reset the new fields are loaded to the default values (compatible with NS32081). Illegal Instruction always causes TRAP and can't be disabled.

#### **CONTROL BITS**

RESERVED OPERANDS ENABLE (ROE bit 17). If this bit is cleared, the FPC requests an Invalid Operation trap whenever a NaN has been detected by the FPC. Infinities are not reserved operands in the FPC. When ROE is disabled, the FPC does not generate reserved operands as results. Denormalized Numbers (DNRM) are always treated as reserved operands. If Invalid Operation or Divide by Zero or Overflow exceptions are disabled, the ROE bit is overwritten internally (the FPC does not change the ROE bit in the FSR) and the FPC can accept or generate quiet NaN as results. ROE bit does not affect MOVf instruction.

INVALID OPERATION ENABLE (IVE bit 18). If this bit is cleared, the FPC requests a trap whenever the operation is invalid. If this bit is set to "1", the trap is disabled and if invalid operation occurred, quiet NaN will be delivered as result.

DIVIDE BY ZERO ENABLE (DZE bit 19). If this bit is cleared the FPC requests a trap whenever an attempt is made to divide by zero. If this bit is set the trap is disabled and if divide by zero occurred, infinity will be delivered as result.

OVERFLOW ENABLE (OVE bit 20). If this bit is cleared, the FPC requests a trap whenever a floating-point result is too big in absolute value to be represented. If this bit is set, the overflow trap is disabled and if overflow occurred, Infinity or Maximum Number will be delivered as result.

INTEGER CONVERSION OVERFLOW ENABLE (IOE bit 21). If this bit is cleared, the FPC requests a trap whenever an Integer result is too big to be represented. If this bit is set, the integer conversion overflow is disabled and if integer conversion overflow occurred, Max/Min integer will be delivered as result.

#### STATUS BITS

RESERVED OPERAND FLAG (ROF bit 22). This bit is set by the FPC whenever reserved operand DNRM or NaN (when ROE is cleared) is selected by the FPC. The ROF bit is "sticky" and can be cleared only by writing a zero with the Load FSR instruction or by a hardware reset.

INVALID FLAG (IVF bit 23). This bit is set by the FPC whenever the operation is invalid. The IVF bit is "sticky" and can be cleared only by writing a zero with the Load FSR instruction or by a hardware reset.

DIVIDE BY ZERO FLAG (DZF bit 24). This bit is set by the FPC whenever an attempt is made to divide a non-zero value by zero. The DZF bit is "sticky" and can be cleared only by writing a zero with the Load FSR instruction or by a hardware reset.

| 31       | 27 | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |  |

|----------|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--|

| Reserved |    | IOF | OVF | DZF | IVF | ROF | IOE | OVE | DZE | IVE | ROE | RMB |  |

FIGURE 2-3. New FSR Mode Control Fields

OVERFLOW (OVF bit 25). This bit is set by the FPC whenever a floating-point result is too large in absolute value to be represented. The OVF bit is "sticky" and can be cleared only by writing a zero with the Load FSR instruction or by a hardware reset.

INTEGER OVERFLOW (IOF bit 26). This bit is set by the FPC whenever an integer result is too large in absolute value to be represented. The IOF bit is "sticky" and can be cleared only by writing a zero with the Load FSR instruction or by a hardware reset.

#### RESERVED FIELD

Bits 31-27 in the FSR are reserved by NSC for future use. User should not use this field.

#### 2.1.2.5 FSR Default Values

During Reset the FSR is loaded to a default value (see Table 2-1). The default values for the FSR represent upward compatibility of the FPC-FPDP with the NS32081. The user can change the default values by loading the FSR register with new values.

**TABLE 2-1. FSR Default State Summary**

| TABLE 2-1. F3h Delauit State Sullimary |                  |                                                                                                      |  |  |  |

|----------------------------------------|------------------|------------------------------------------------------------------------------------------------------|--|--|--|

| Bit Name                               | Default<br>Value | Default State                                                                                        |  |  |  |

| TT (bits 2-0)                          | 0                | No exceptional condition occurred.                                                                   |  |  |  |

| UEN (bit 3)                            | 0                | Underflow trap disabled.                                                                             |  |  |  |

| UF (bit 4)                             | 0                | Underflow flag is cleared.                                                                           |  |  |  |

| IEN (bit 5)                            | 0                | Inexact result trap disabled.                                                                        |  |  |  |

| IF (bit 6)                             | 0                | Inexact flag is cleared.                                                                             |  |  |  |

| RM (bits 8-7)                          | 0                | Round to nearest.                                                                                    |  |  |  |

| SWF (bits 15-9)                        | 0                |                                                                                                      |  |  |  |

| RMB (bit 16)                           | 0                | RMB flag is cleared.                                                                                 |  |  |  |

| ROE(bit 17)                            | 0                | FPC requests a trap whenever an attempt is made to use reserved operand except for MOVf instruction. |  |  |  |

| IVE (bit 18)                           | 0                | FPC requests a trap whenever the operation is invalid.                                               |  |  |  |

| DZE (bit 19)                           | 0                | FPC requests a trap whenever an attempt is made to divide by zero.                                   |  |  |  |

| OVE (bit 20)                           | 0                | FPC requests a trap whenever a floating-point result is too big to be represented.                   |  |  |  |

| IOE (bit 21)                           | 0                | FPC requests a trap whenever an integer conversion result is too big to be represented.              |  |  |  |

| ROF (bit 22)                           | 0                | ROF flag is cleared.                                                                                 |  |  |  |

TABLE 2-1. FSR Default State Summary (Continued)

| Bit Name                 | Default<br>Value | Default State              |  |  |  |

|--------------------------|------------------|----------------------------|--|--|--|

| IVF (bit 23)             | 0                | IVF flag is cleared.       |  |  |  |

| DZF (bit 24)             | 0                | DZF flag is cleared.       |  |  |  |

| OVF (bit 25)             | 0                | OVF flag is cleared.       |  |  |  |

| IOF (bit 26)             | 0                | IOF flag is cleared.       |  |  |  |

| RESERVED<br>(bits 31-27) | 0                | Reserved field is cleared. |  |  |  |

#### 2.2 INSTRUCTION SET

#### 2.2.1 General Instruction Format

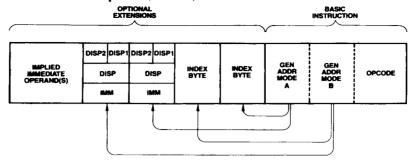

Figure 2-4 shows the general format of a Series 32000 instruction. The Basic Instruction is one to three bytes long and contains the opcode and up to two 5-bit General Addressing Mode (Gen) fields. Following the Basic Instruction field is a set of optional extensions, which may appear depending on the instruction and the addressing modes selected.

The only form of extension issued to the NS32580 FPC is an Immediate operand. Other extensions are used only by the CPU to reference memory operands needed by the FPC.

Index Bytes appear when either or both Gen fields specify Scaled Index. In this case, the Gen field specifies only the Scale Factor (1, 2, 4 or 8), and the Index Byte specifies which General Purpose Register to use as the index, and which addressing mode calculation to perform before indexing. See Figure 2-5.

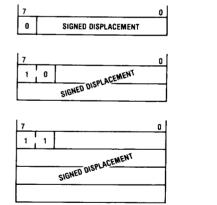

Following Index Bytes come any displacements (addressing constants) or immediate values associated with the selected addressing modes. Each Disp/Imm field may contain one or two displacements, or one immediate value. The size of a Displacement field is encoded within the top bits of that field, as shown in *Figure 2-6*, with the remaining bits interpreted as a signed (two's complement) value. The size of an immediate value is determined from the Opcode field. Both Displacement and Immediate fields are stored most significant byte first.

Some non-FPC instructions require additional, "implied" immediates and/or displacements, apart from those associated with addressing modes. Any such extensions appear at the end of the instruction, in the order that they appear within the list of operands in the instruction definition.

#### 2.2.2 Addressing Modes

The Series 32000 Family CPUs generally access an operand by calculating its Effective Address based on information available when the operand is to be accessed. The method to be used in performing this calculation is specified by the programmer as an "addressing mode."

Addressing modes in the Series 32000 family are designed to optimally support high-level language accesses to variables. In nearly all cases, a variable access requires only

FIGURE 2-4. General Instruction Format

TL/FE/9421-2

one addressing mode within the instruction which acts upon that variable. Extraneous data movement is therefore minimized.

Series 32000 Addressing Modes fall into nine basic types:

**Register:** In floating-point instructions, these addressing modes refer to a Floating-Point Register (F0-F7) or (L0-L7) if the operand is of a floating-point type. Otherwise, a CPU General Purpose Register (R0-R7) is referenced. See Section 2.1.1.

**Register Relative:** A CPU General Purpose Register contains an address to which is added a displacement value from the instruction, yielding the Effective Address of the operand in memory.

| 7 |                 | 3 | 2       | 0 |

|---|-----------------|---|---------|---|

|   | GEN. ADDR. MODE |   | REG. NO |   |

FIGURE 2-5. Index Byte Format

TL/EE/9421-3

**Memory Space:** Identical to Register Relative above, except that the register used is one of the dedicated CPU registers PC, SP, SB or FP. These registers point to data areas generally needed by high-level languages.

**Memory Relative:** A pointer variable is found within the memory space pointed to by the CPU SP, SB or FP register. A displacement is added to that pointer to generate the Effective Address of the operand.

Immediate: The operand is encoded within the instruction. This addressing mode is not allowed if the operand is to be written. Floating-point operands as well as integer operands may be specified using Immediate mode.

**Absolute:** The address of the operand is specified by a Displacement field in the instruction.

**External:** A pointer value is read from a specified entry of the current Link Table. To this pointer value is added a displacement, yielding the Effective Address of the operand.

**Top of Stack:** The currently-selected CPU Stack Pointer (SP0 or SP1) specifies the location of the operand. The operand is pushed or popped, depending on whether it is written or read.

Scaled Index: Although encoded as an addressing mode, Scaled Indexing is an option on any addressing mode except Immediate or another Scaled Index. It has the effect of calculating an Effective Address, then multiplying any General Purpose Register by 1, 2, 4 or 8 and adding it into the total, yielding the final Effective Address of the operand.

The following table, Table 2-2, is a brief summary of the addressing modes. For a complete description of their actions, see the Series 32000 Instruction Set Reference Manual.

TL/EE/9421-4

FIGURE 2-6. Displacement Encodings

| Encoding    | Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Assembler Syntax             | Effective Address                           |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------------|

| REGISTER    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                            |                                             |

|             | Pagistor 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R0, F0 or L0                 | None: Operand is in the specified registe   |

| 00000       | Register 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R1, F1 or L1                 | 140116. Operand is in the specified registe |

| 00001       | Register 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R1, F1 or L1<br>R2, F2 or L2 |                                             |

| 00010       | Register 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                              |                                             |

| 00011       | Register 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R3, F3 or L3                 |                                             |

| 00100       | Register 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R4, F4 or L4                 |                                             |

| 00101       | Register 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R5, F5 or L5                 |                                             |

| 00110       | Register 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R6, F6 or L6                 |                                             |

| 00111       | Register 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R7, F7 or L7                 |                                             |

| REGISTER RE | LATIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                              |                                             |

| 01000       | Register 0 relative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | disp(R0)                     | Disp + Register.                            |

| 01001       | Register 1 relative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | disp(R1)                     |                                             |

| 01010       | Register 2 relative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | disp(R2)                     |                                             |

| 01011       | Register 3 relative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | disp(R3)                     |                                             |

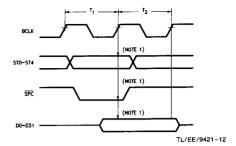

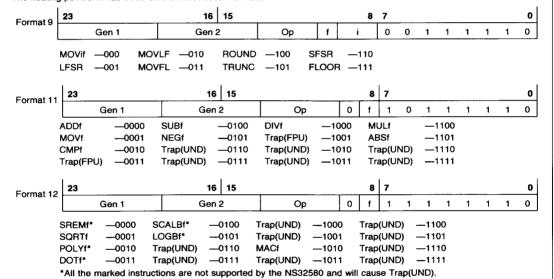

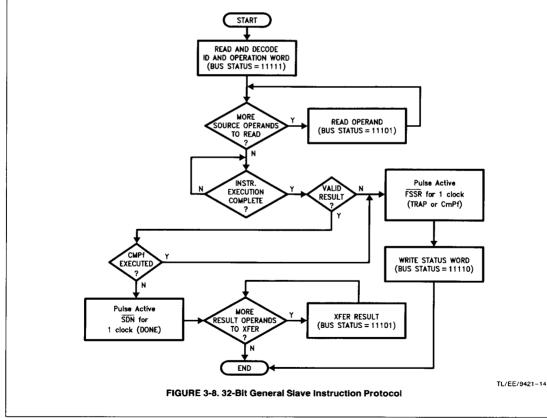

| 01100       | Register 4 relative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | disp(R4)                     |                                             |